Improve FPGA, ASIC and SoC Quality with Early Architecture Modeling

Jack Erickson

# Video Series: Range-Doppler Radar System Deployment

MathWorks® Products Solutions Academia Support Community Events

Video and Webinar Series

Videos Home Search

Developing Radio Applications for RFSoC with MATLAB &

Simulink

### Part 1: Hardware/Software Co-Design Workflow

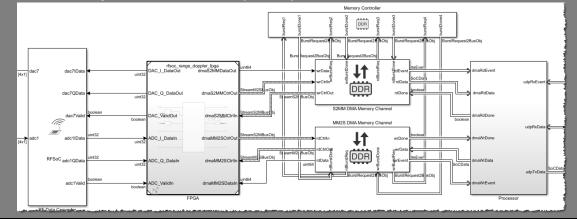

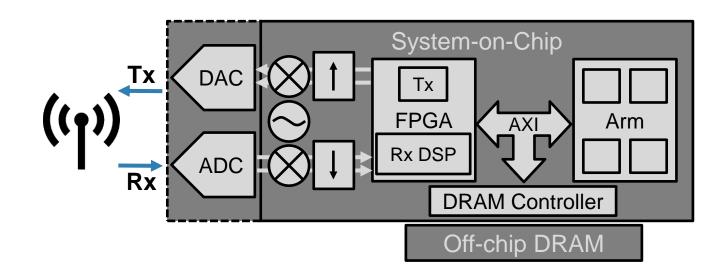

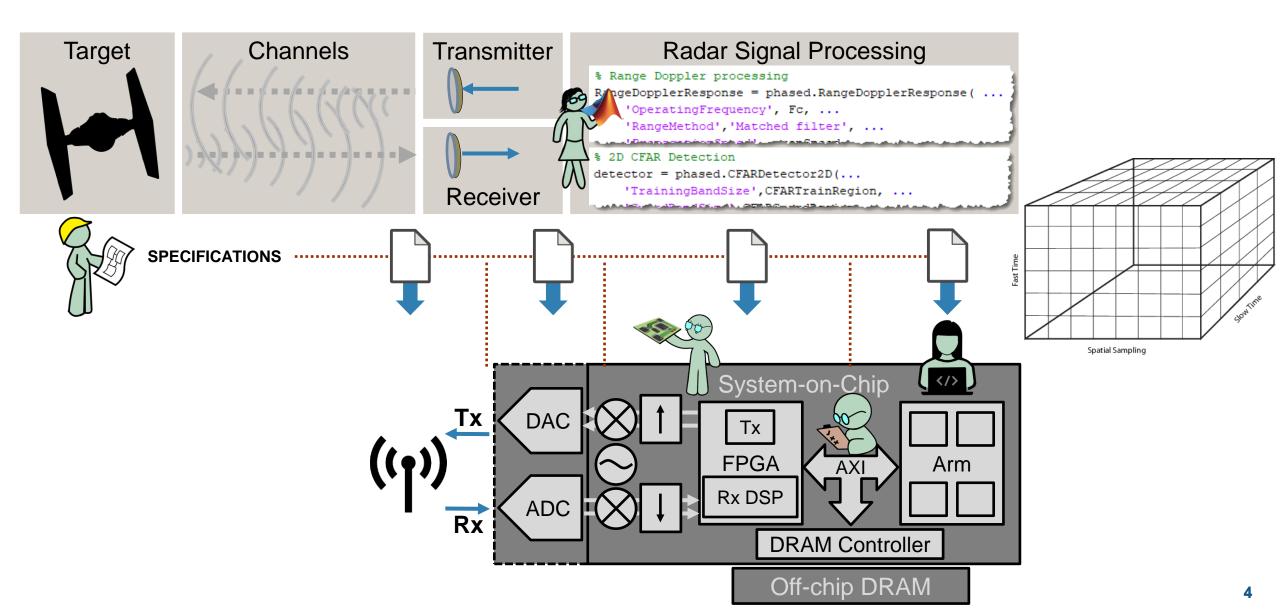

Target SoC architectures like Xilinx UltraScale+ RFSoC devices using Model-Based Design. Build Simulink models of hardware/software platforms to make design decisions.

### Part 2: System Specification and Design

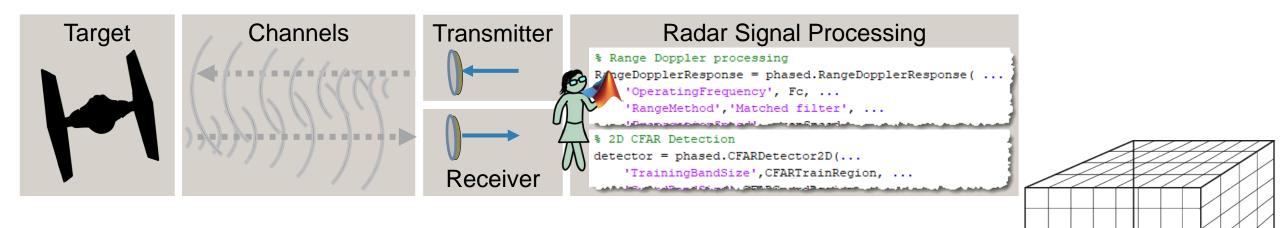

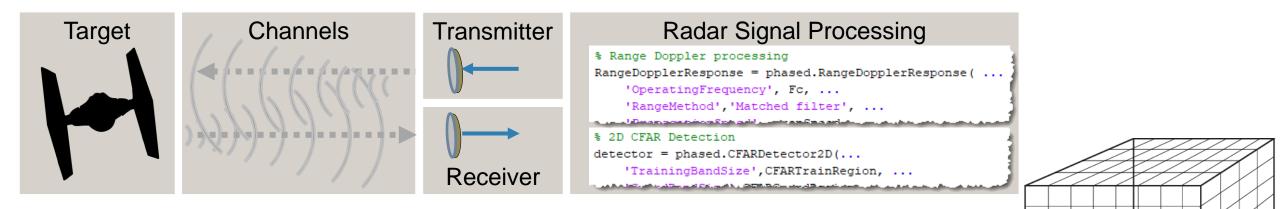

System specifications for a range-Doppler radar are the driver for hardware/software implementation decisions when targeting SoC architectures like Xilinx RFSoC devices.

### Part 3: Hardware/Software Partitioning

Perform simulation and analysis of the SoC architecture of the Xilinx RFSoC to investigate hardware/software partitioning of the range-Doppler radar algorithm.

### Part 4: Code Generation and Deployment

Use SoC Blockset to automate the process of C and HDL code generation from Simulink models, and to automatically deploy the range-Doppler radar algorithm to a Xilinx ZCU111 development kit.

System-on-Chip Implementation Model

Spatial Sampling

# Range-Doppler Radar: System & Algorithm vs. Implementation

# Range-Doppler Radar: System & Algorithm vs. Implementation

# Range-Doppler Radar: System & Algorithm vs. Implementation

# Poll: Which Role Do You Play? (select all that apply)

System Designer/Architect

Domain Expert / Algorithms (DSP, comms, radar, controls, video/image, etc)

Hardware Designer (FPGA or ASIC)

**FPGA/ASIC** Verification Engineer

Embedded Software Developer

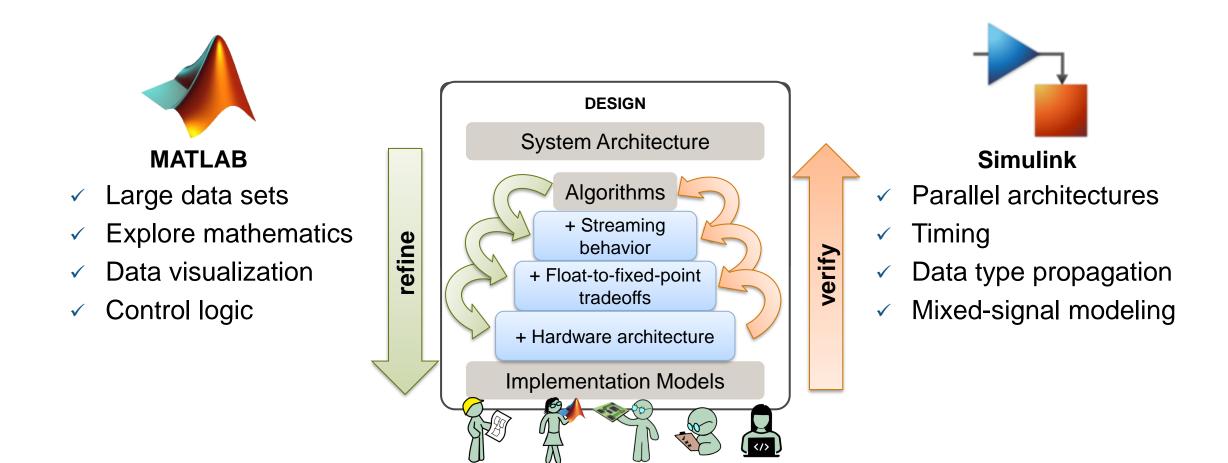

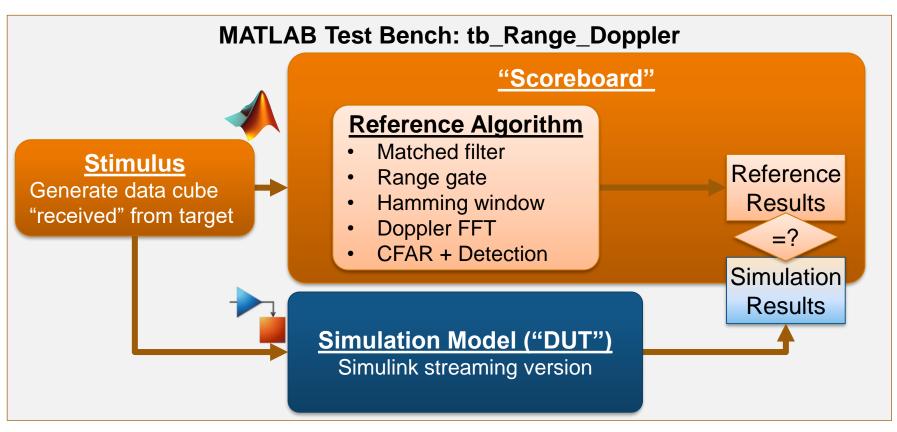

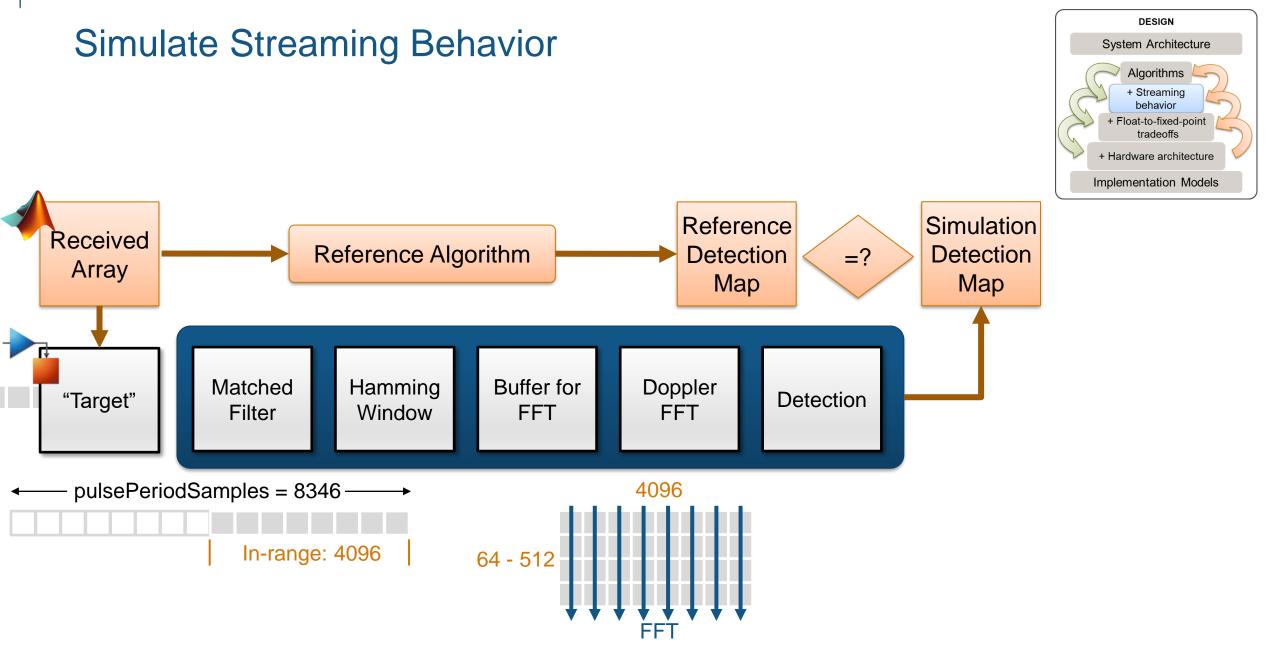

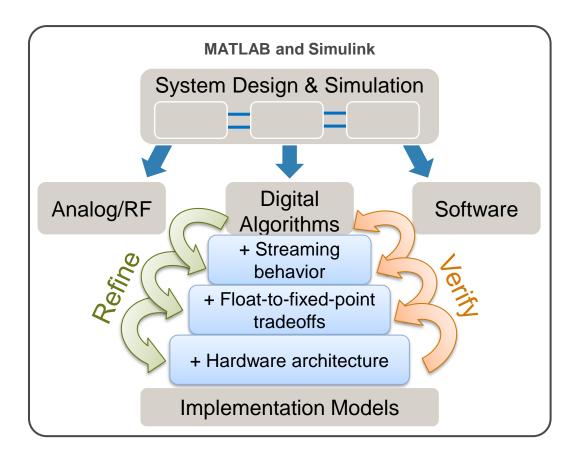

# **Top-Down Refinement and Verification**

All roles contribute to key early decisions and continuously integrate

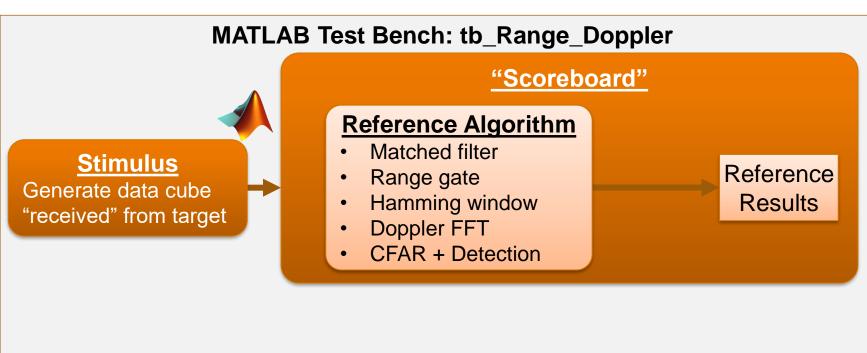

# **Algorithm Partitioning**

# **Algorithm Partitioning**

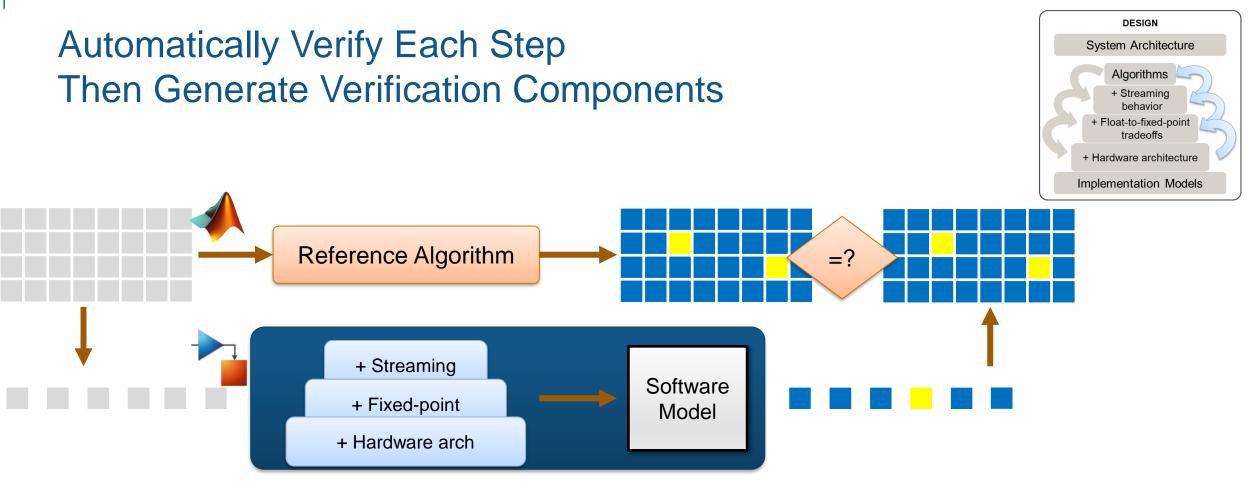

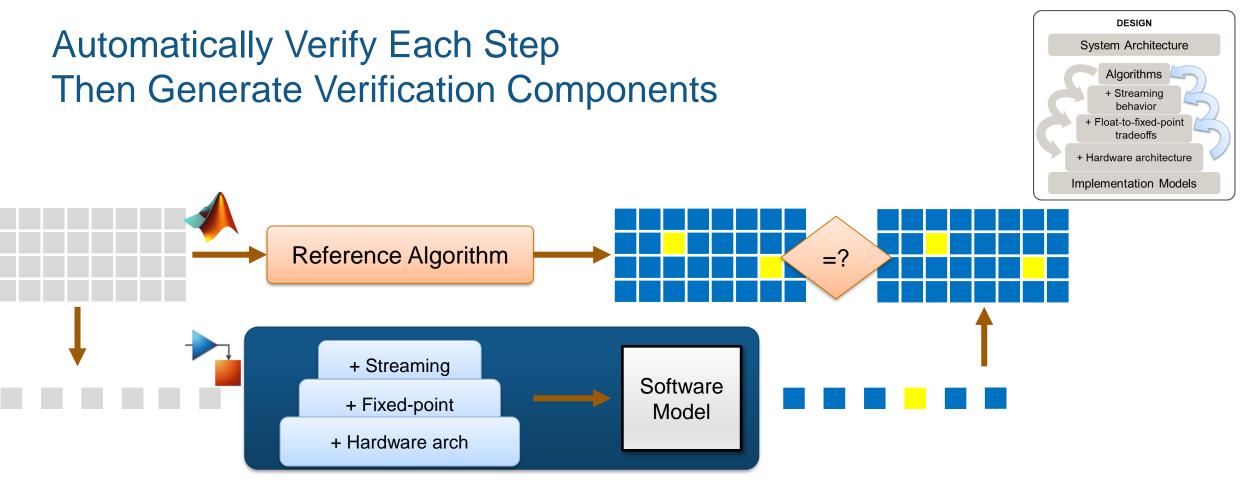

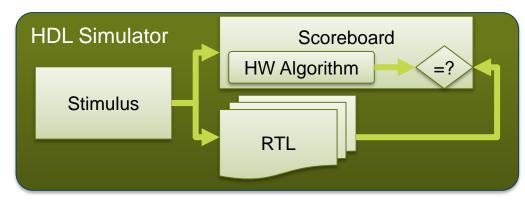

- ✓ Robust self-checking back-to-back testing

- ✓ Generate verification components

- SystemVerilog DPI-C (via MATLAB Coder)

- ✓ Re-use functions for future projects

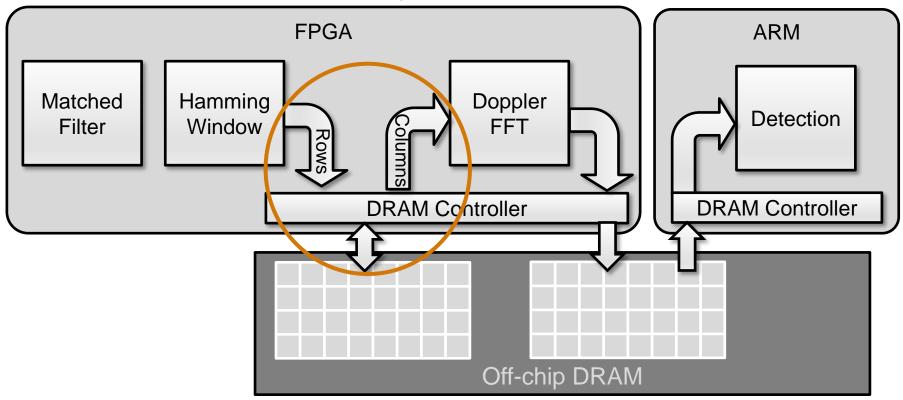

# **Option A: Implement FFT in Hardware**

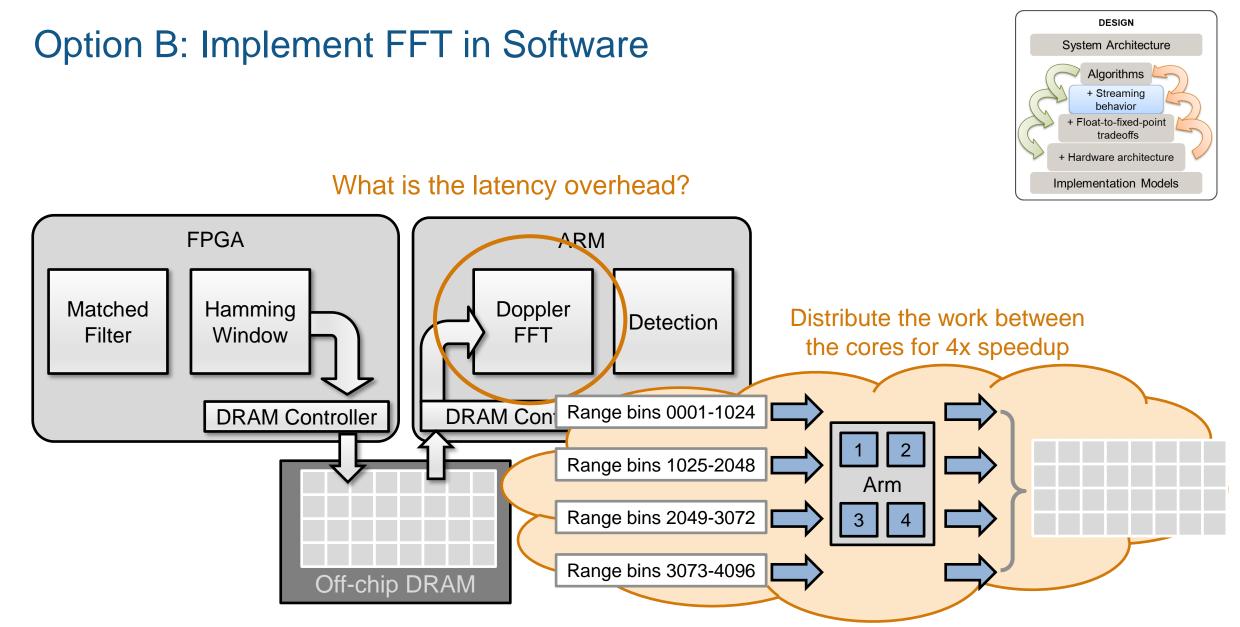

# What is the latency overhead?

# Analyze Option A

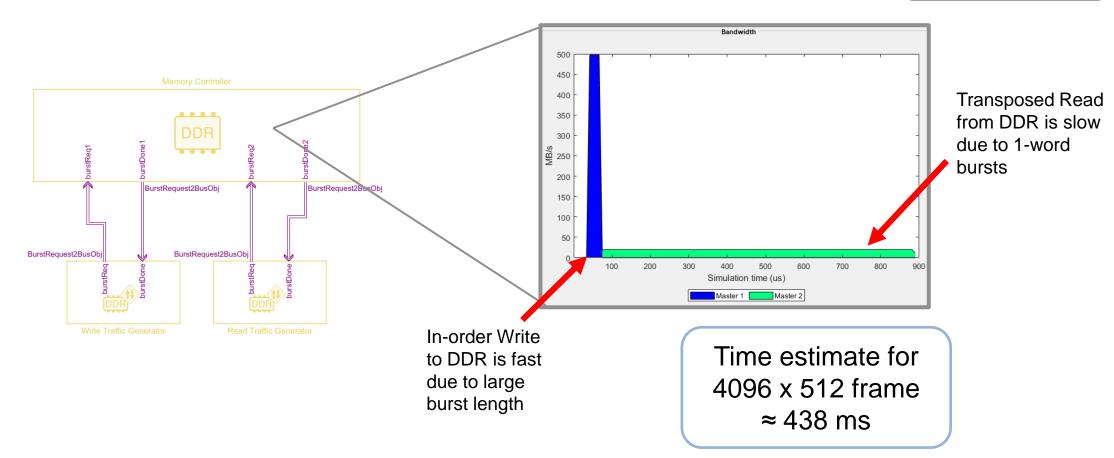

- Estimate DDR transpose timing with Memory Traffic Generators

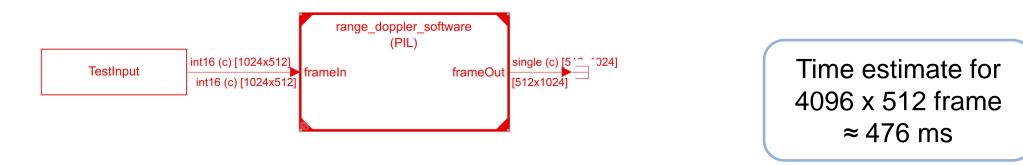

Use Processor in the Loop (PIL) profiling to analyze timing

Analyze Option B

| Section                            | Maximum<br>Execution<br>Time in ns | Average<br>Execution<br>Time in ns | Maximum<br>Self Time in<br>ns | Average Self<br>Time in ns | Calls |

|------------------------------------|------------------------------------|------------------------------------|-------------------------------|----------------------------|-------|

| range_doppler_softwa_initialize    | 860                                | 860                                | 860                           | 860                        | 1 📰 📣 |

| [-] range_doppler_software [0.1 0] | 478714177                          | 475864990                          | 2550                          | 2236                       | 5 📰 📣 |

| <u>Transpose</u>                   | 83062620                           | 81849649                           | 83062620                      | 81849649                   | 5 📰 📣 |

| DTC                                | 23243053                           | 21569826                           | 23243053                      | 21569826                   | 5 📰 📣 |

| [+] <u>FFT</u>                     | 372470295                          | 372443279                          | 1550                          | 1426                       | 5 📰 📣 |

|          | Method       | Latency | Complexity |

|----------|--------------|---------|------------|

| Option A | FPGA FFT     | 438 ms  | High       |

| Option B | Software FFT | 476 ms  | Low        |

**Compare Options**

Poll: Which option would you choose?

17

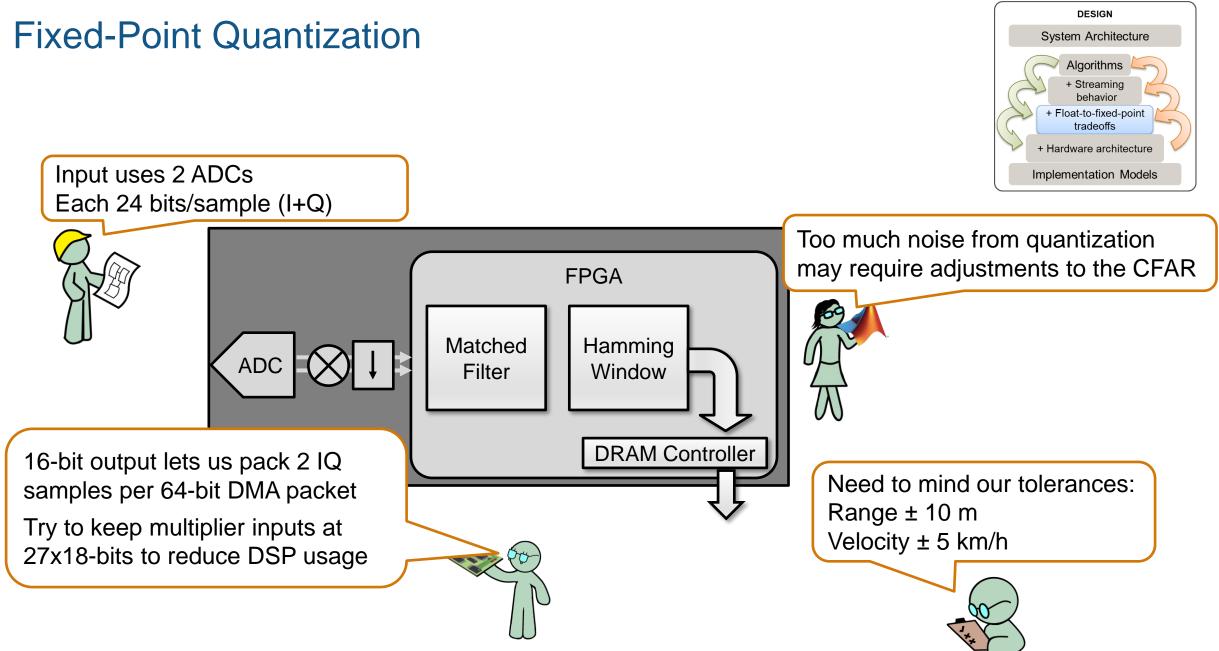

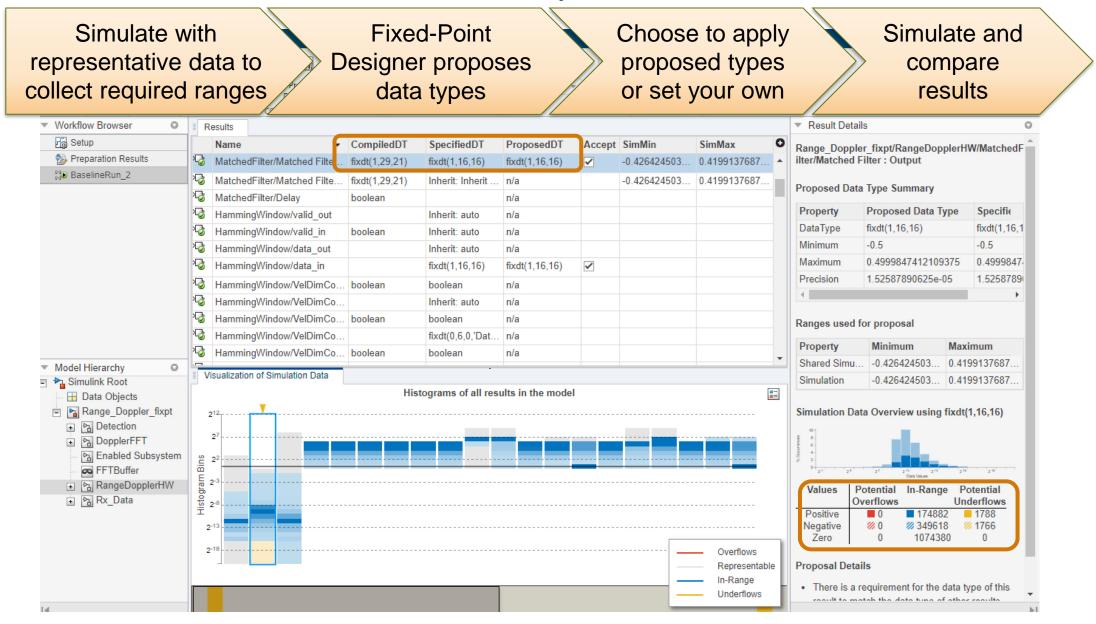

# **Explore and Simulate Quantization Options**

Generate SystemVerilog DPI/UVM verification test bench components

- ✓ Executable specification no miscommunication

- ✓ Change the model, re-simulate and re-generate

- ✓ Saves RTL verification time/effort

# Collaborate on Top-Down Refinement and Verification

- All roles contribute to high-level design and exploration

- Eliminate costly system-level bugs early

- Communicate via executable models

- Generate stimuli and scoreboards for verification

- Simulink helps system architects and hardware designers communicate. It is like a shared language that enables us to exchange knowledge, ideas, and designs.

Marcel van Bakel Philips Healthcare

|             | Qualcomm | Prototype Platform for Imaging Applications                                                |  |

|-------------|----------|--------------------------------------------------------------------------------------------|--|

| MATLAB EXPO | Cadence  | Accelerating Design, Data Visualization and<br>Analysis of Analog and Mixed-Signal Systems |  |

|             | NI       | SDR Solutions with NI Hardware and<br>MathWorks Software                                   |  |

# Video Series

# Developing Radio Applications for RFSoC with MATLAB & Simulink

### Part 1: Hardware/Software Co-Design Workflow

Target SoC architectures like Xilinx UltraScale+ RFSoC devices using Model-Based Design. Build Simulink models of hardware/software platforms to make design decisions.

### Part 2: System Specification and Design

System specifications for a range-Doppler radar are the driver for hardware/software implementation decisions when targeting SoC architectures like Xilinx RFSoC devices.

### Part 3: Hardware/Software Partitioning

Perform simulation and analysis of the SoC architecture of the Xilinx RFSoC to investigate hardware/software partitioning of the range-Doppler radar algorithm.

### Part 4: Code Generation and Deployment

Use SoC Blockset to automate the process of C and HDL code generation from Simulink models, and to automatically deploy the range-Doppler radar algorithm to a Xilinx ZCU111 development kit.

# **Products and Solutions**

HDL Code Generation and Verification MATLAB for FPGA, ASIC, and SoC Development HDL Coder HDL Verifier Fixed-Point Designer SoC Blockset

# Thank you

© 2021 The MathWorks, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.