Accelerating Design, Data Visualization and Analysis of **Analog and Mixed-Signal Systems**

Steven Lewis, Jesson John

MATLAB EXPO 2021

### Agenda

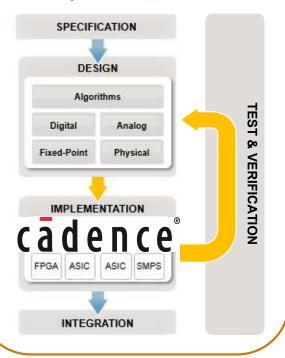

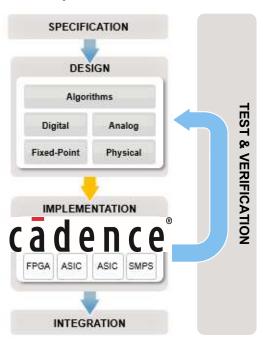

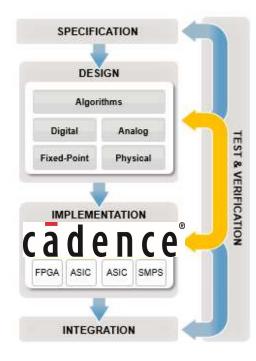

Mixed-Signal Design & Verification

- Cadence design platform

- MATLAB/Simulink

- Mixed-signal blockset

Integrated Workflows with Cadence

- Data post-processing (mixed-signal analyzer app)

- Code generation (SystemVerilog model export from Simulink)

- Co-simulation of mixed-signal systems with Simulink and Cadence Virtuoso AMS Designer

Summary

- Customer testimonial

- · How to get started

- Q & A

# Problem Statement: How do you ...?

How do you Design this?

How do you Analyze this?

How do you Implement this?

How do you Verify this?

Analog and RF Blocks

Mixed-Signal Blocks

Discrete Components and Memories

Packages and Board(s)

How do you know when you are done?

What's the common answer to all of these questions?

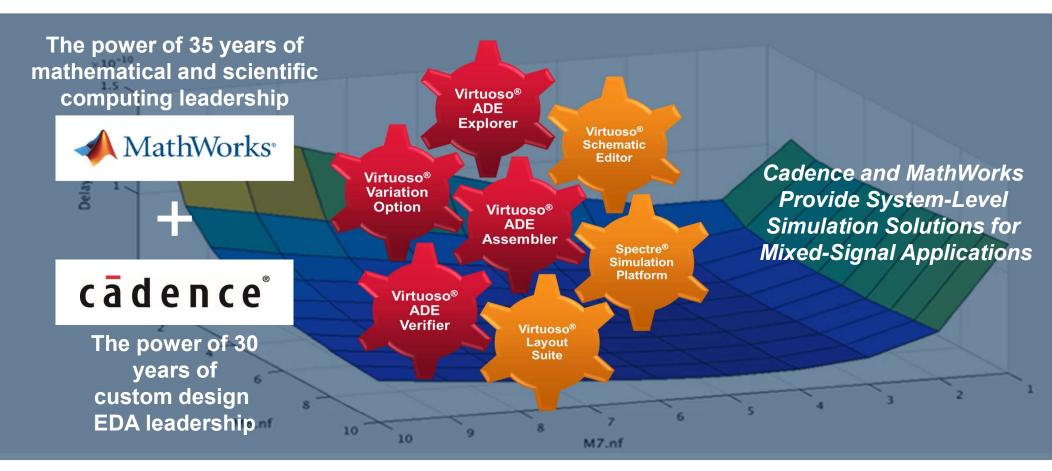

Cadence and MathWorks Partnership

#### Experience Bridges the Divide Between ICs and Systems

Extensive relationship with MathWorks relationship

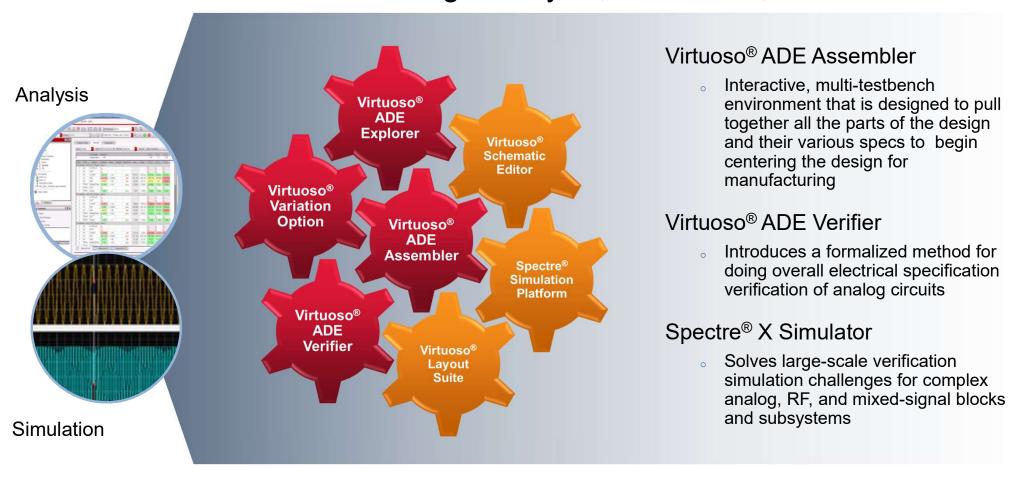

### Under the Hood - Breakthrough Analysis, Simulation, and Verification

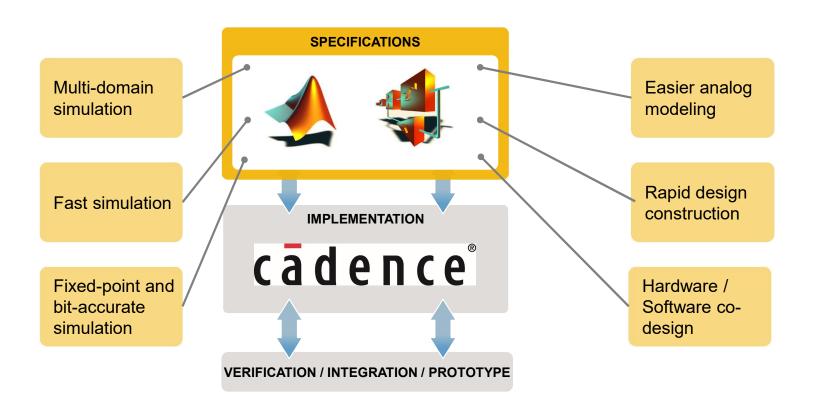

### Mixed-Signal Design and Analysis with MATLAB and Simulink

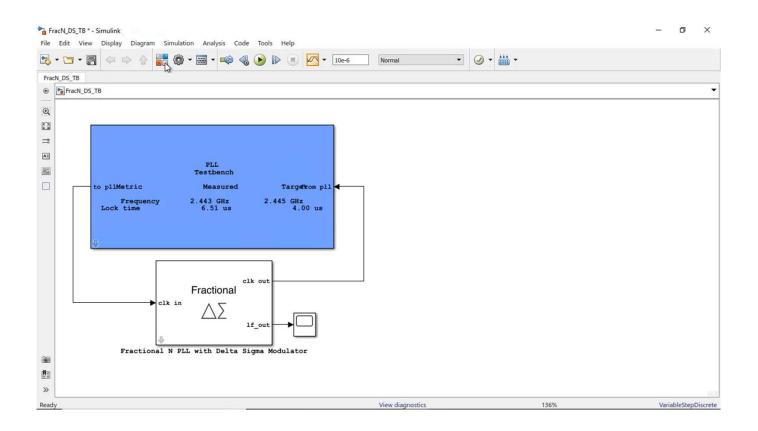

Focus on Simulation and Model Refinement at the System Level

# Mixed-Signal Blockset

Design, Simulate, and Analyze Analog and Mixed-Signal Systems

### Agenda

Mixed-Signal Design & Verification

- Cadence design platform

- MATLAB/Simulink

- Mixed-signal blockset

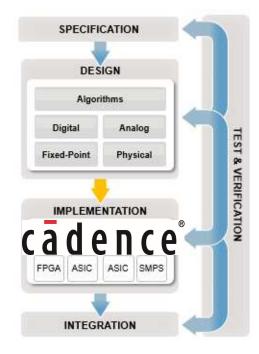

Integrated Workflows with Cadence

- Data post-processing (mixed-signal analyzer app)

- Code generation (SystemVerilog model export from Simulink)

- Co-simulation of mixed-signal systems with MATLAB and Simulink

Summary

- Customer testimonial

- How to get started

- Q & A

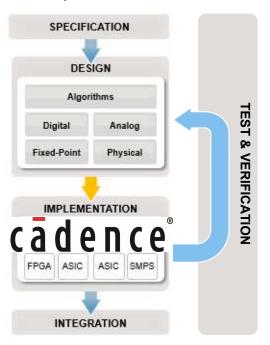

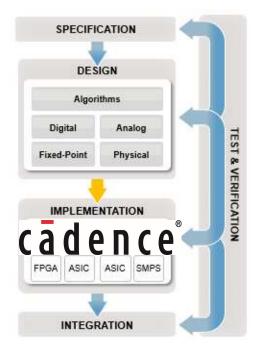

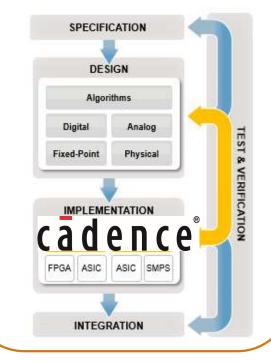

### Cadence MATLAB/Simulink Integration Workflows

#### **Data Post Processing**

- Analyze trends in data

- Compare simulations

- Report & Document

#### Code generation

- Testbench generation

- Regression testing

#### Co-simulation

- Debugging

- Validation of behavioral models

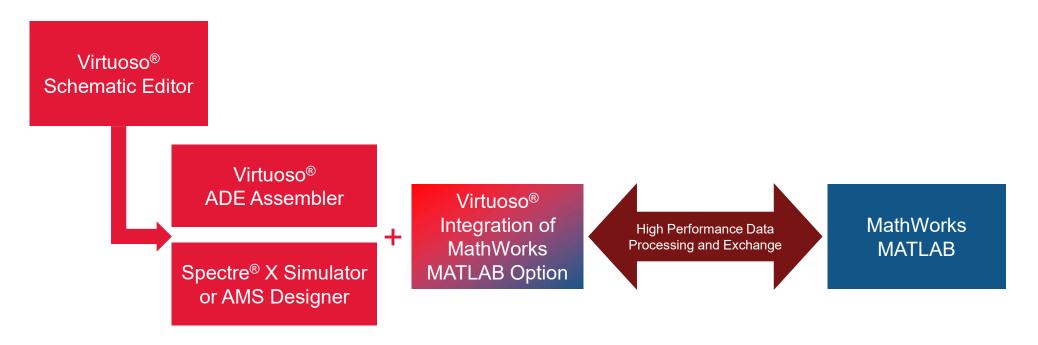

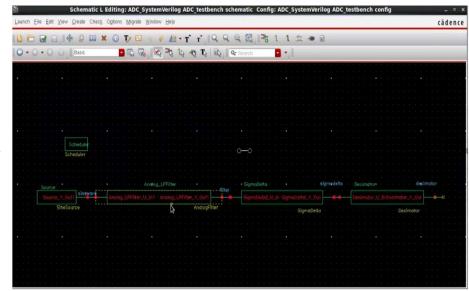

# Overview of the Integration

Using MathWorks MATLAB for large data-processing

Standard design input methods including the creation of design tests inside Virtuoso ADE Assembler/Verifier. These tests can include MATLAB expressions or make calls to MATLAB scripts for post-processing. The expressions and tests are simulated by Spectre X or AMS Design simulators.

MATLAB can read and produce the same simulation database as ADE and ViVA. MATLAB can be launched in a real time mode from within ADE for on the fly data-processing.

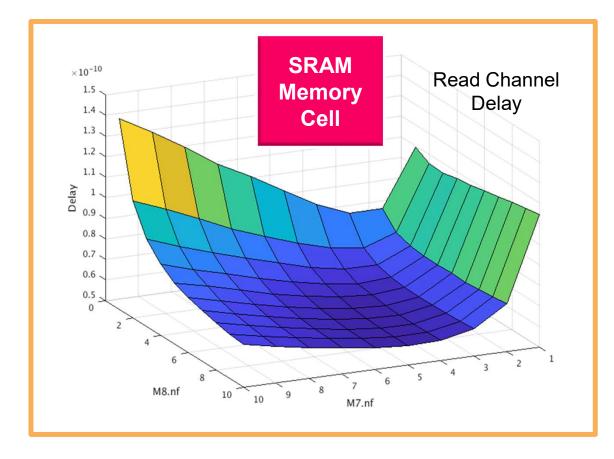

# Quickly Determine Trade-offs Even When Using Gigabytes of Data

MATLAB / Virtuoso ADE Product Suite integration

Q: What is the impact on the read channel delay if I change the size of my transistors?

A: Simulate the design in Virtuoso® ADE and visualize the trade-off results in MathWork's MATLAB

MATLAB EXPO

# Mixed Signal Analyzer Demo

Cadence-MATLAB Integration Workflow

D

1

### Cadence MATLAB/Simulink Integration Workflows

#### **Data Post Processing**

- Analyze trends in data

- Compare simulations

- Report & Document

#### Code generation

- Testbench generation

- Regression testing

#### Co-simulation

- Debugging

- Validation of behavioral models

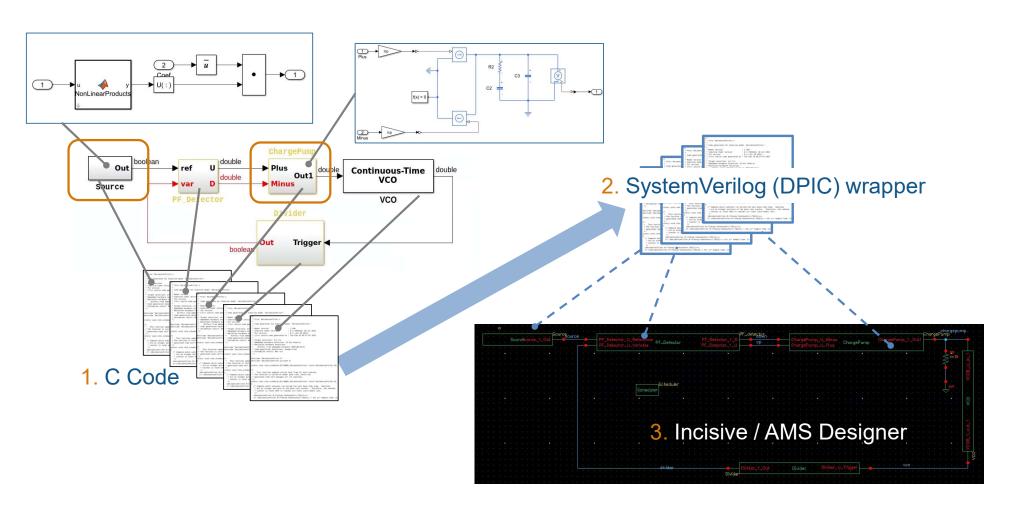

# SystemVerilog Model Export from Simulink/MATLAB (1)

What is the benefit of this workflow?

# SystemVerilog Model Export from Simulink/MATLAB (2)

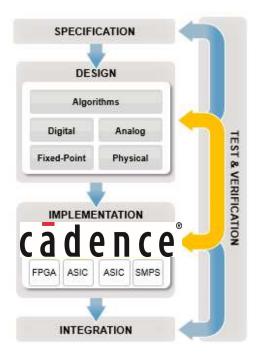

### Cadence MATLAB/Simulink Integration Workflows

#### **Data Post Processing**

- Analyze trends in data

- Compare simulations

- Report & Document

#### Code generation

- Testbench generation

- Regression testing

#### Co-simulation

- Debugging

- Validation of behavioral models

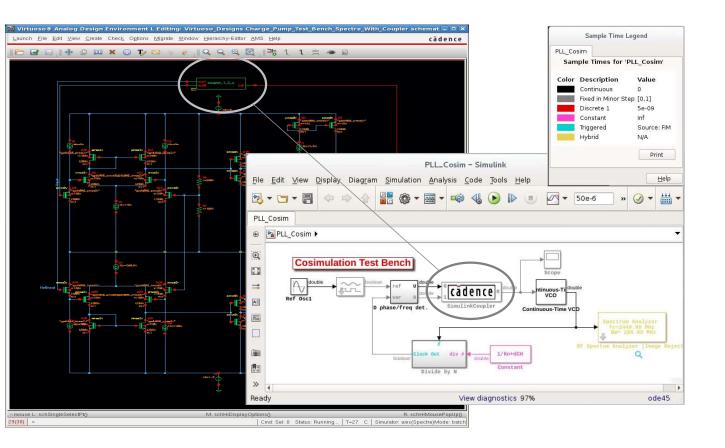

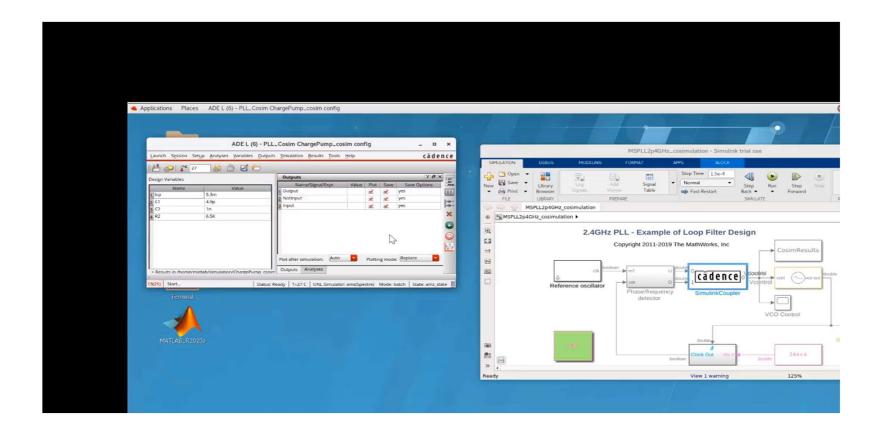

# Verification of Circuit Design: Analog Co-simulation

# Verification of Circuit Design: Analog Co-simulation (2)

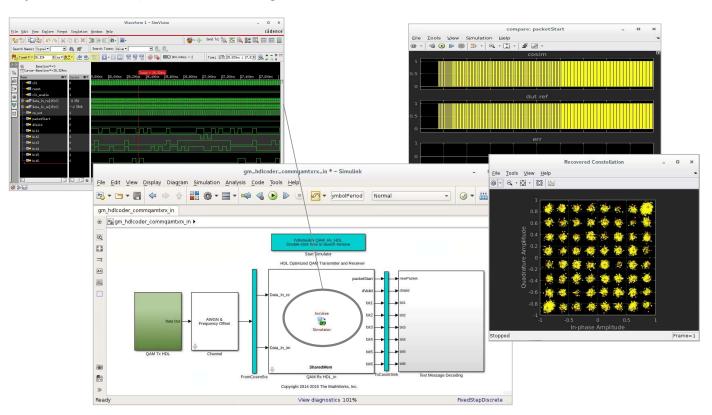

# Verification of Circuit Design: Digital Co-simulation

Verify the HDL implementation against the executable specifications

### Agenda

Mixed-Signal Design & Verification

- Cadence design platform

- MATLAB/Simulink

- Mixed-signal blockset

Integrated Workflows with Cadence

- Data post-processing (mixed-signal analyzer app)

- Code generation (SystemVerilog model export from Simulink)

- Co-simulation of mixed-signal systems with MATLAB and Simulink

Summary

- Customer testimonial

- How to get started

- Q & A

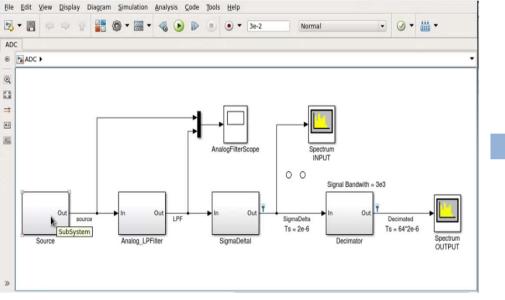

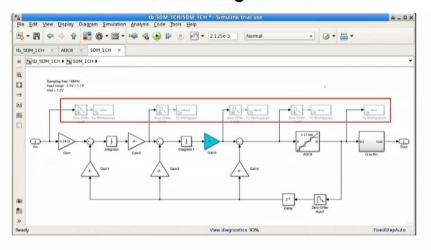

### Mixed-Signal Model-Based Design Flow for Automotive Sensors

#### Simulink Analog Models using DPI-C: Continuous Time Sigma Delta ADC

Make sure and "comment out" any elements in the subsystem that you do not want in the generated code.

Those elements are shown inside the red box.

For 15 years, Cadence's Virtuoso and MATLAB from MathWorks have been our tools of choice for automotive ASIC sensor development. Now that the MATLAB and Virtuoso platforms are inherently compatible, we can easily move between environments and utilize the powerful capabilities of each solution. With ever-increasing product complexity and aggressive schedules, the integration enables thorough verification in the analog domain so that we can meet our time-sensitive deadlines.

- Jamie Haas, Director of Design Engineering, Allegro Microsystems

Mixed-Signal Model-Based

Design Flow for Automotive

Sensors

# Summary

- Cadence and MathWorks integrated workflows for design, visualization and verification of mixedsignal systems.

- MATLAB + Cadence for data post-processing w/ mixed-signal analyzer app

- SystemVerilog model export from MATLAB/Simulink into Cadence

- Analog/Digital co-simulation with Simulink + Cadence

### How to get started

- Useful resources

- MATLAB & Simulink for Mixed-Signal Systems

- Cadence Virtuoso ADE MATLAB Integration Option

- Mixed-Signal Blockset

- Mixed-Signal Analyzer app

- SystemVerilog Model Export for AMS Verification

- Co-simulation with Cadence and Simulink

- Hands-on Analog Mixed-Signal Workshop

- Delivered via AWS cloud (at no cost)

- Virtuoso ADE + MATLAB Integration Rapid Adoption Kit available from Cadence

# MATLAB EXPO 2021

Thank you

© 2021 The MathWorks, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See *mathworks.com/trademarks* for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders