# MATLAB EXPO 2019

Adopting Model-Based Design for FPGA, ASIC, and SoC Development

Fahd Morchid

### Agenda

- Why Model-Based Design for FPGA, ASIC, or SoC?

- Case Study Pulse Detector

- HW/SW Co-Design

- Customer results

### Agenda

- Why Model-Based Design for FPGA, ASIC, or SoC?

- Case Study Pulse Detector

- HW/SW Co-Design

- Customer results

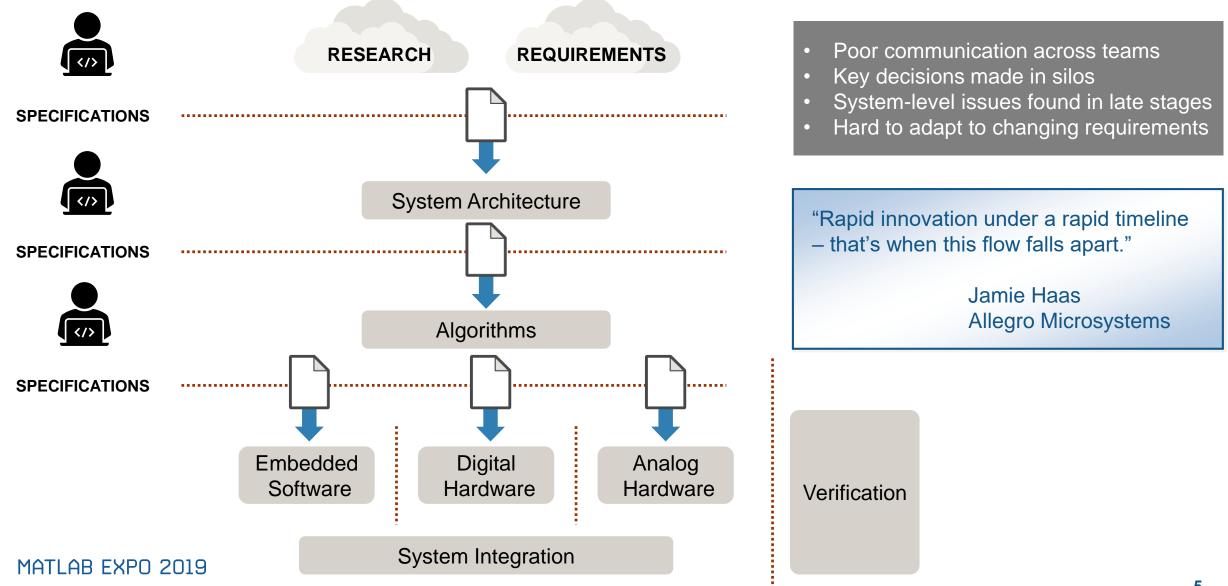

### FPGA, ASIC, and SoC Development Projects

67% of ASIC/FPGA projects are behind schedule

Over 50% of project time is spent on verification

75% of ASIC projects require a silicon re-spin

| 2009 |    |    | 2020 |    |    |

|------|----|----|------|----|----|

| Q1   | Q2 | Q3 | Q4   | Q1 | Q2 |

|      |    |    |      |    |    |

|      |    |    |      |    |    |

|      |    |    |      |    |    |

|      |    |    |      |    |    |

|      |    |    |      |    |    |

MATLAB EXPO 2019

# 84% of FPGA projects have non-trivial bugs escape into production

Statistics from 2018 Mentor Graphics / Wilson Research survey, averaged over FPGA/ASIC

### Many Different Skill Sets Need to Collaborate

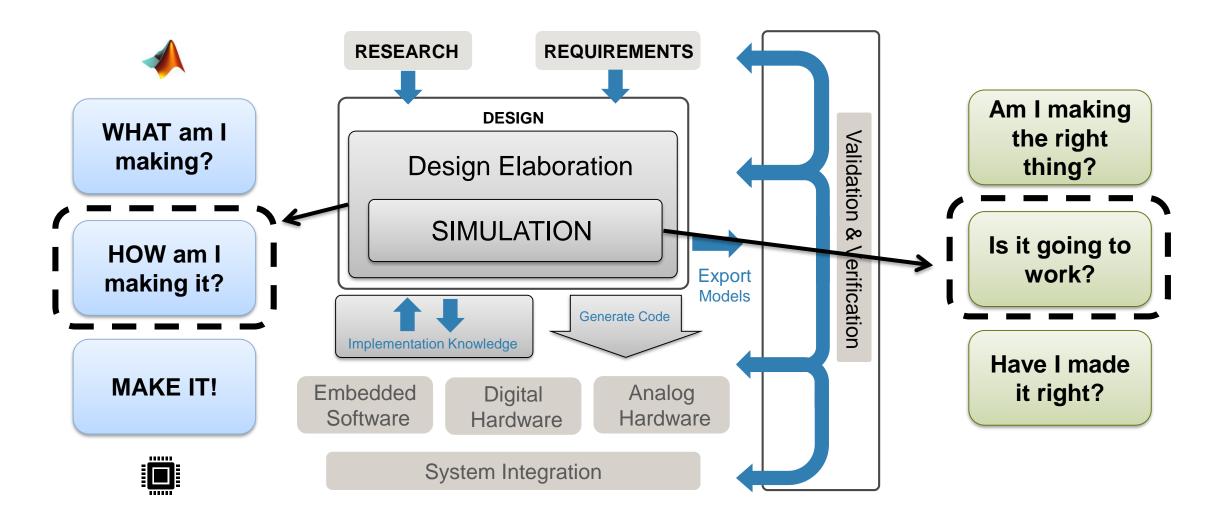

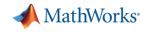

### **SoC Collaboration with Model-Based Design**

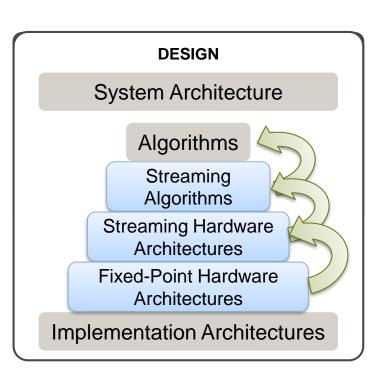

### **General Approach: Use the Strengths of MATLAB and Simulink**

- Large data sets

- Explore mathematics

- ✓ Control logic

- Data visualization

- Parallel architectures

- Timing

- Data type propagation

- Mixed-signal modeling

### Agenda

- Why Model-Based Design for FPGA, ASIC, or SoC?

- Case Study Pulse Detector

- HW/SW Co-Design

- Customer results

- 1. Example Overview

- 2. Reference Pulse Detector

- 3. Pulse Detector Design

- 4. Prepare for Hardware Implementation

- 5. Fixed-point Conversion

- 6. HDL code generation, synthesis and verification

### 1. Example Overview

- 2. Reference Pulse Detector

- 3. Pulse Detector Design

- 4. Prepare for Hardware Implementation

- 5. Fixed-point Conversion

- 6. HDL code generation, synthesis and verification

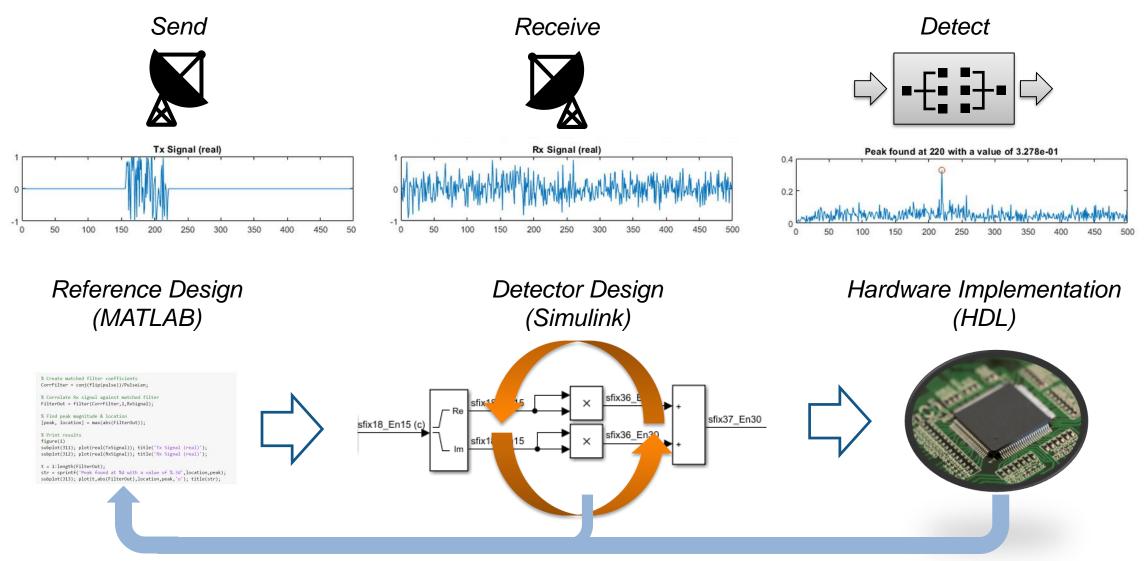

### Pulse Detector | Overview

- 1. Example Overview

- 2. Reference Pulse Detector

- 3. Pulse Detector Design

- 4. Prepare for Hardware Implementation

- 5. Fixed-point Conversion

- 6. HDL code generation, synthesis and verification

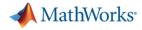

| Algorithm<br>Stimulus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reference<br>Algorithm                                                                                                                                                                                                                                                            | Software<br>Algorithm Analysis                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Create input stimulus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MATLAB golden reference                                                                                                                                                                                                                                                           | 1 Tx Signal (real)                                           |

| <pre>function [ CorrFilter, RxSignal, RxFxPt ] = pulse_detector_stim % Create pulse to detect rng('default'); PulseLen = 64; theta = rand(PulseLen,1); pulse = exp(1i*2*pi*theta); % Insert pulse to Tx signal rng('shuffle'); TxLen = 5000; PulseLoc = randi(TxLen-PulseLen*2); TxSignal = complex(zeros(TxLen,1)); TxSignal(PulseLoc:PulseLoc+PulseLen-1) = pulse; % Create Rx signal by adding noise Noise = complex(randn(TxLen,1),randn(TxLen,1)); RxSignal = TxSignal + Noise; % Scale Rx signal to +/- one scale1_=_max(Labs(real(RxSignal)):.ebs(imag(RxSignal))]);</pre> | <pre>% Create matched filter coefficients<br/>CorrFilter = conj(flip(pulse))/PulseLen;<br/>% Correlate Rx signal against matched filter<br/>FilterOut = filter(CorrFilter,1,RxSignal);<br/>% Find peak magnitude &amp; location<br/>[peak, location] = max(abs(FilterOut));</pre> | $     \begin{array}{c}                                     $ |

14

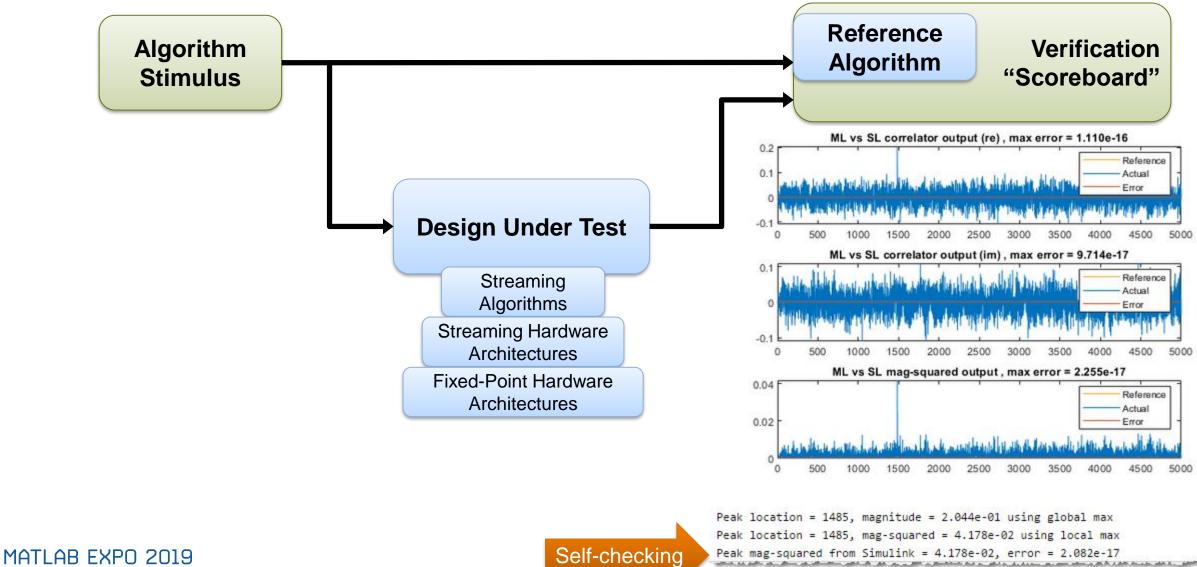

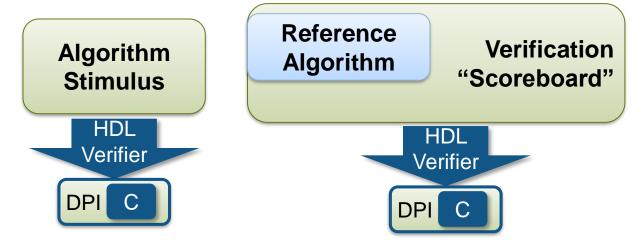

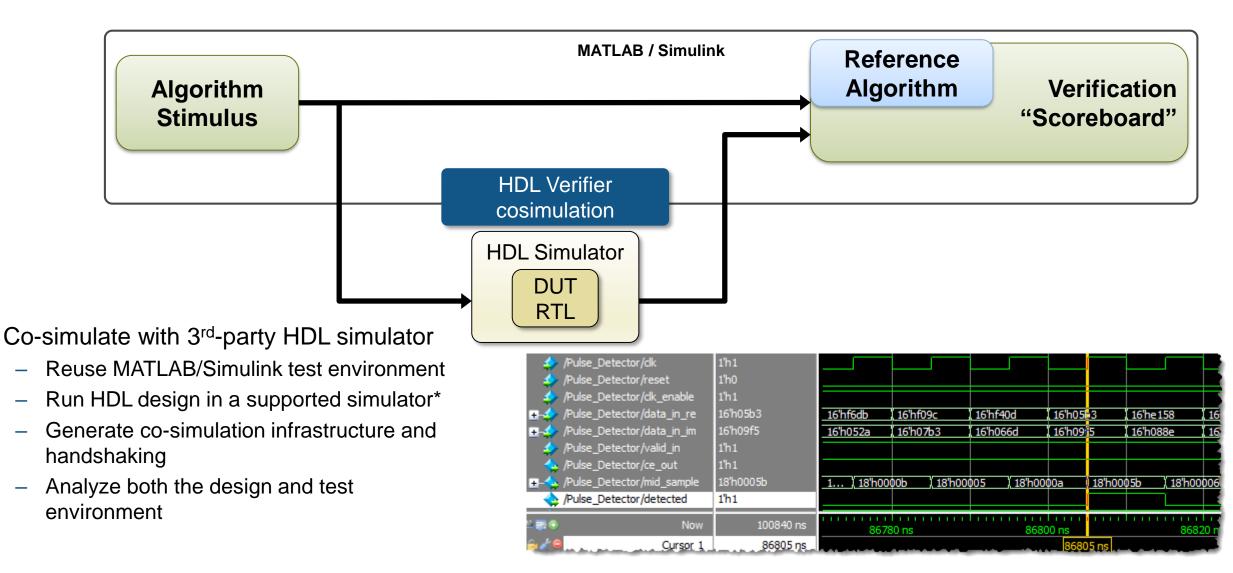

- Reuse MATLAB/Simulink models in verification

- Scoreboard, stimulus, or models external to the RTL

- Runs natively in SystemVerilog simulator

- Eliminate re-work and miscommunication

- Save testbench development time

- Easy to update when requirements change

#### MATLAB EXPO 2019

\* Mentor Graphics<sup>®</sup> ModelSim<sup>®</sup> or Questa<sup>®</sup> Cadence<sup>®</sup> Incisive<sup>®</sup> or Xcelium<sup>™</sup>

- 1. Example Overview

- 2. Reference Pulse Detector

- 3. Pulse Detector Design

- 4. Prepare for Hardware Implementation

- 5. Fixed-point Conversion

- 6. HDL code generation, synthesis and verification

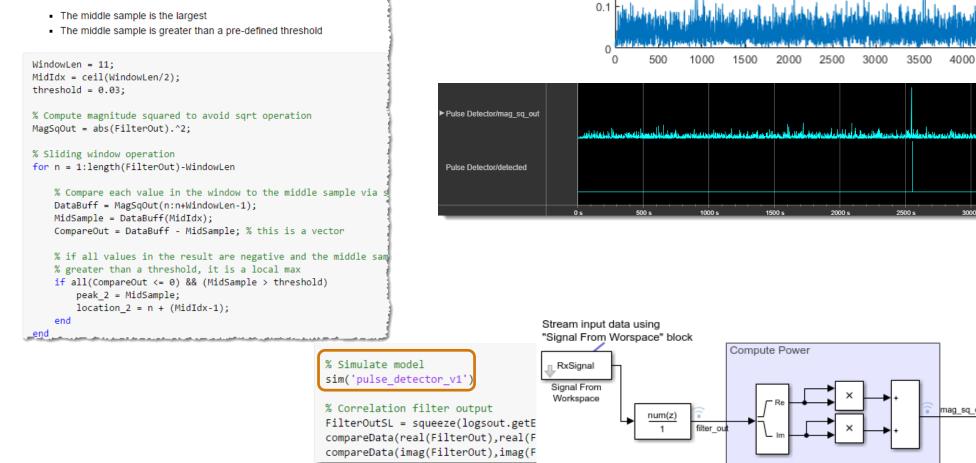

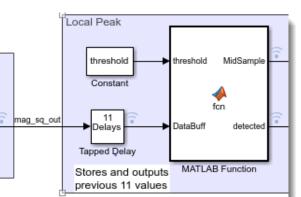

### Pulse Detector | Design in Simulink Streaming Architecture

#### Hardware friendly implementation of peak finder

Instead of calculating the maximum value of the entire frame, we look for a local peak within a sliding window of the last 11 samples using the following criteria:

0.2

4000

5000

4500

Peak found at 2060 with a value of 2.007e-01

| _dev_AG (snapshot_centos_20190510) [En fonction] - Oracle VM VirtualBox : 1                                                  |             |

|------------------------------------------------------------------------------------------------------------------------------|-------------|

| fachine Écran Entrée Périphériques Aide                                                                                      |             |

|                                                                                                                              | 📰 🍉 🌠 🔚 🚛 🔔 |

| pulse_detector_streaming_arch * - Simulink                                                                                   |             |

| it <u>V</u> iew <u>D</u> isplay Diag <u>r</u> am <u>S</u> imulation <u>A</u> nalysis <u>C</u> ode <u>T</u> ools <u>H</u> elp |             |

| □ • 📄 < □ ↔ ↔ 🔛 <<br>                                                                                                        |             |

| se_detector_streaming_arch                                                                                                   |             |

| Papulse_detector_streaming_arch >                                                                                            |             |

- 1. Example Overview

- 2. Reference Pulse Detector

- 3. Pulse Detector Design

- 4. Prepare for Hardware Implementation

- 5. Fixed-point Conversion

- 6. HDL code generation, synthesis and verification

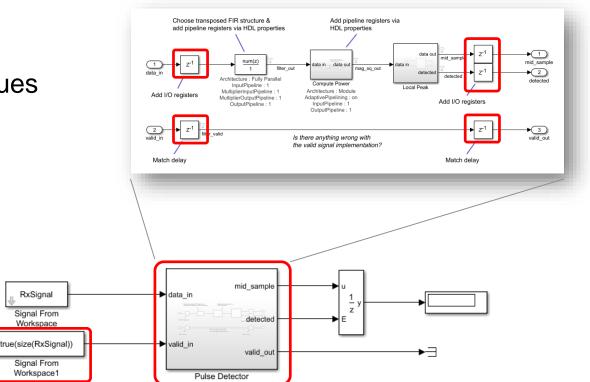

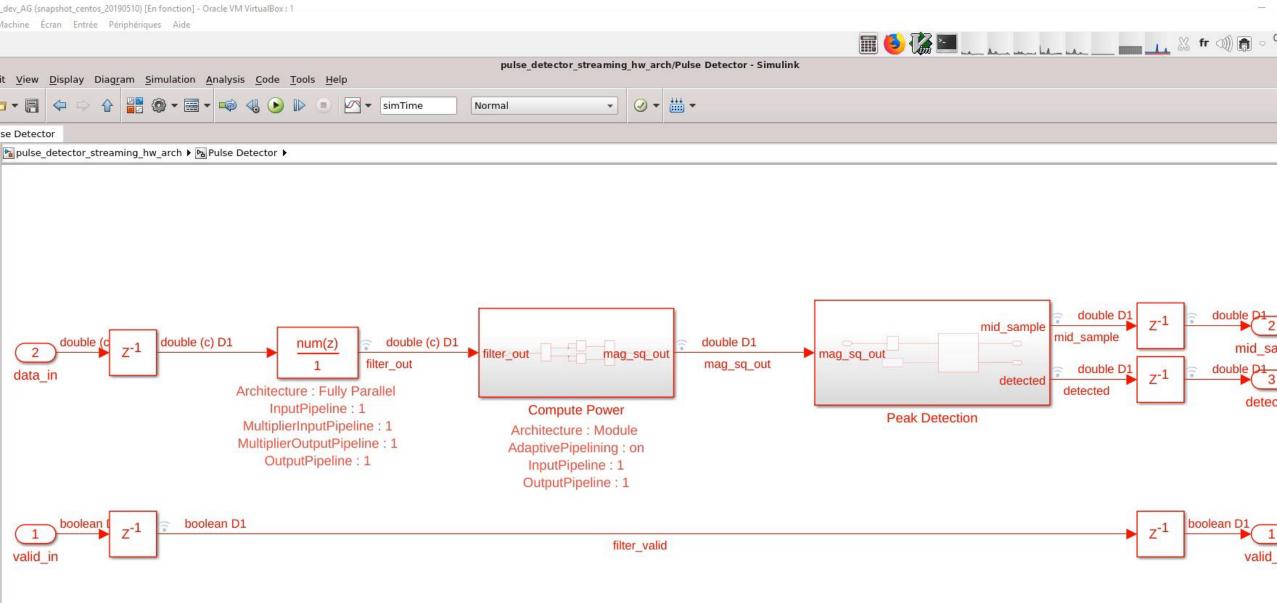

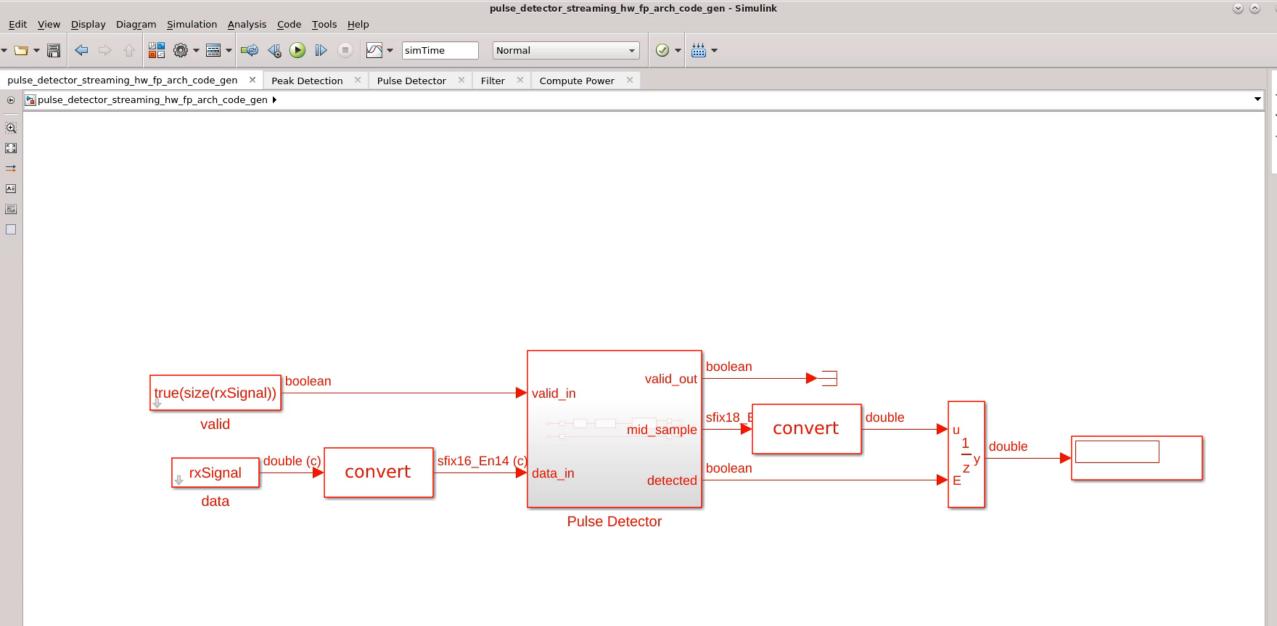

### Pulse Detector | Prepare for Hardware Design Micro Architecture

In this step, we:

- prepare the model for HDL code generation

- pipeline the data path using various techniques

- add data valid control signal

- verify against MATLAB golden reference

Ъ

- 1. Example Overview

- 2. Reference Pulse Detector

- 3. Pulse Detector Design

- 4. Prepare for Hardware Implementation

- 5. Fixed-point Conversion

- 6. HDL code generation, synthesis and verification

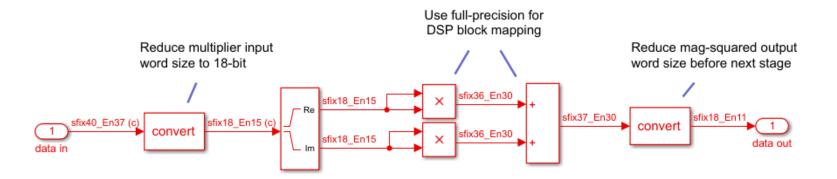

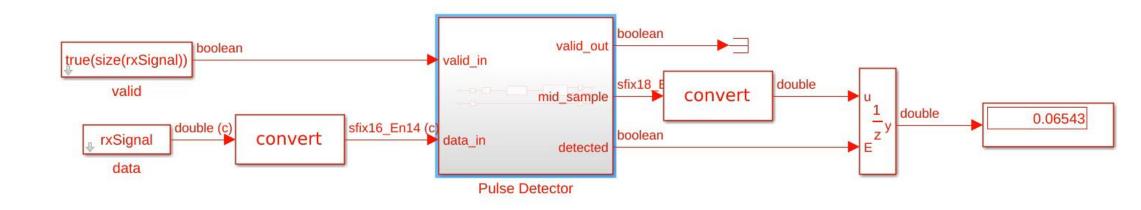

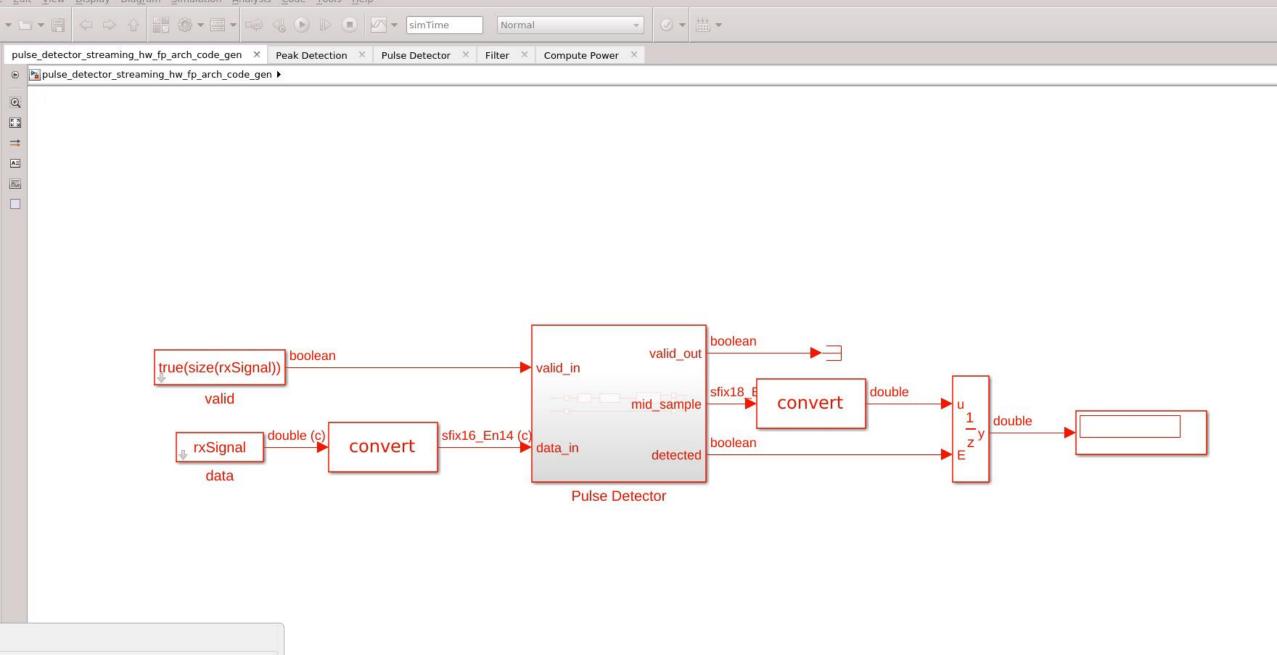

### Pulse Detector | Fixed-Point Conversion

In this step, we:

convert the model to fixed-point

compare the Simulink fixed-point model to the MATLAB golden reference

| _dev_AG (snapshot_centos_20190510) [En fonction] - Oracle VM VirtualBox : 1                                                  | -                            |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| fachine Écran Entrée Périphériques Aide                                                                                      |                              |

|                                                                                                                              | 📰 🥌 🌠 🔤 🔜 🐰 fr 🐠 👼 🗸         |

|                                                                                                                              | eaming_hw_fp_arch - Simulink |

| it <u>V</u> iew <u>D</u> isplay Diag <u>r</u> am <u>S</u> imulation <u>A</u> nalysis <u>C</u> ode <u>T</u> ools <u>H</u> elp |                              |

| □ • 📄 💠 ↔ 🔐 🎯 • 📾 • 🕫 🍕 🕑 🕪 💿 🖉 • simTime Normal •                                                                           |                              |

| se_detector_streaming_hw_fp_arch                                                                                             |                              |

| Papulse_detector_streaming_hw_fp_arch >                                                                                      |                              |

2

Ъ

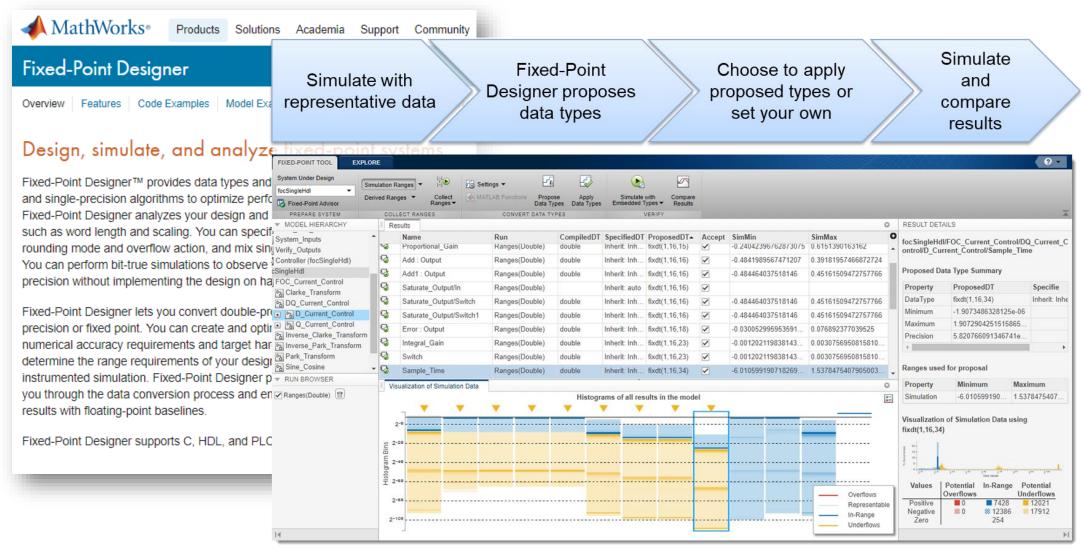

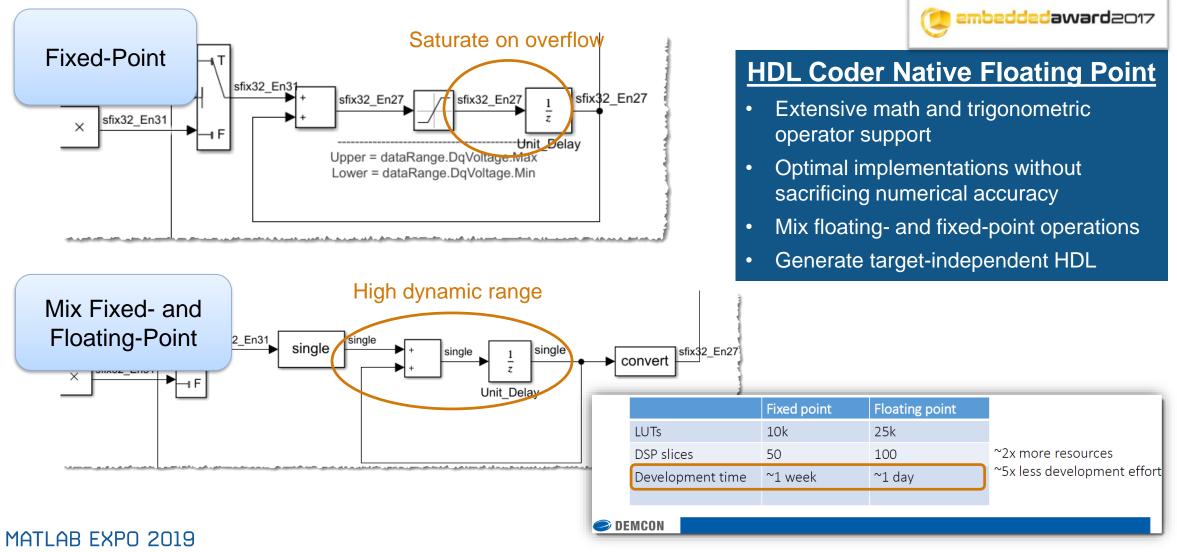

## Some words about Fixed-Point conversion...

### Fixed-Point Conversion | Automated Approach

### **Fixed-Point Conversion** | *Native Floating-Point*

- 1. Example Overview

- 2. Reference Pulse Detector

- 3. Pulse Detector Design

- 4. Prepare for Hardware Implementation

- 5. Fixed-point Conversion

- 6. HDL code generation, synthesis and verification

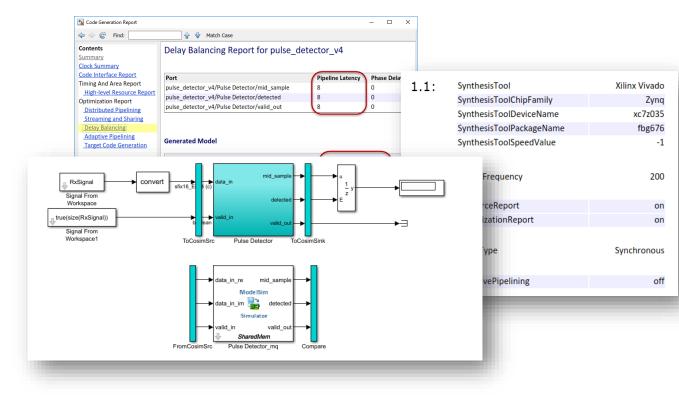

### **Pulse Detector** | HDL Code Generation and Verification

In this step, we:

generate HDL code and reports

synthesize the design using Xilinx Vivado

verify the design

#### Eate view Display Diagram Diminiation Analysis Code 10013 (101)

dy

####

HDL Workflow Advisor - pulse\_detector\_streaming\_hw\_fp\_arch\_code\_gen/Pulse Detector

▼ ⊘ ▼ ₩ ▼

$\odot$   $\otimes$  -

| pul | se_detector_streaming_hw_f | File  | Edit Run Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----|----------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ۲   | 눰 pulse_detector_streaming | Find: | · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|     |                            | •     | HDL Workflow Advisor<br>1. Set Target<br>1. Set Target Trequency<br>1.2. Set Target Frequency<br>2. Prepare Model For HDL Code Genera<br>2.1. Check Global Settings<br>2.2. Check Algebraic Loops<br>2.3. Check Block Compatibility<br>2.4. Check Sample Times<br>3.1 HDL Code Generation<br>3.1. Set Code Generation Options<br>3.1.2. Set Report Options<br>3.1.3. Set Advanced Options<br>3.1.4. Set Optimization Options<br>3.1.4. Set Optimization Options<br>3.3. Verify with HDL Cosimulation<br>3.3. Verify with HDL Cosimulation<br>4.1. Create Project<br>4.2. Perform Synthesis and P/R<br>4.2.1. Run Synthesis<br>4.3. Annotate Model with Synthesis<br>4.3. Annotate Model with Synthesis | S.1.5. Set Testbench Options  Test Bench Generation Output  HDL test bench Sostemverliog DPI test bench Simulation tool: Mentor Graphics Modelsim  HDL code coverage  Configuration  Test bench name postfix: tb  for ce clock Clock high time (ns): 5 Clock witme (ns): 5 Clock witme (ns): 5 Clock witme (ns): 2 Setup time (ns): 2 Setup time (ns): 8 Clock enable Clock enabl |  |

|     |                            |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

Normal

## Is there more?

\_hw\_fp\_arch\_code\_gen \* - Simulink

ulse\_detector\_streaming\_hw\_fp\_arch\_code\_gen/Pulse Detector

- Example Overview

Reference Pulse Detector

Pulse Detector Design

Prepare for Hardware Impleme

Fixed-point Conversion

- 6. HDL code generation, synthesis and verification

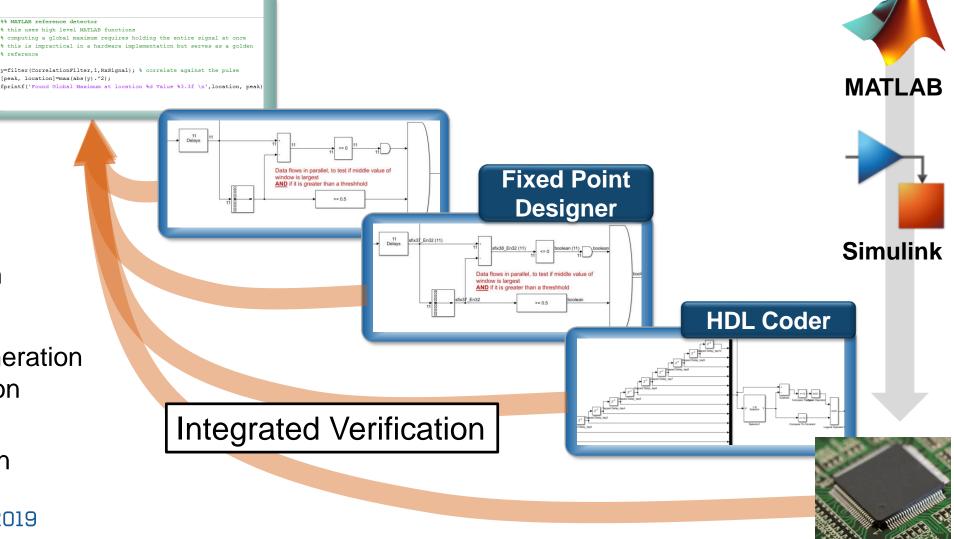

### **Case Study | Workflow Summary**

Hardware Architecture

Fixed-point Implementation

HDL Code Generation and Optimization

reference

**HDL** Verification and Targeting MATLAB EXPO 2019

# A few more words about code generation ...

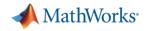

### **Automatically Generate Production RTL**

- Choose from over 300 supported blocks

- Including MATLAB functions and Stateflow charts

- Quickly explore implementation options

- Generate readable, traceable Verilog/VHDL

- Optionally generate AXI interfaces with IP core

- Production-proven across a variety of applications and FPGA, ASIC, and SoC targets

38

### Agenda

- Why Model-Based Design for FPGA, ASIC, or SoC?

- Case Study Pulse Detector

- HW/SW Co-Design

- Customer results

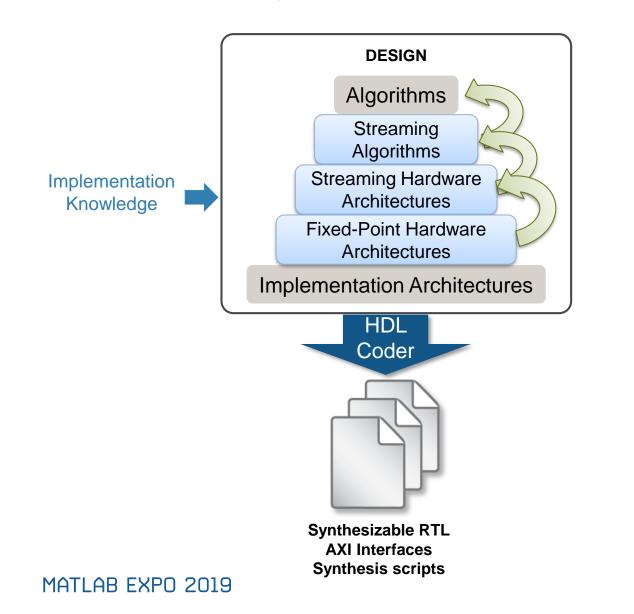

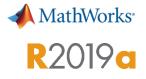

### **HW/SW Design**

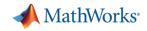

## Model Based Design Workflow for SoC

**Deploy to Hardware with Coders and HW Support Package**

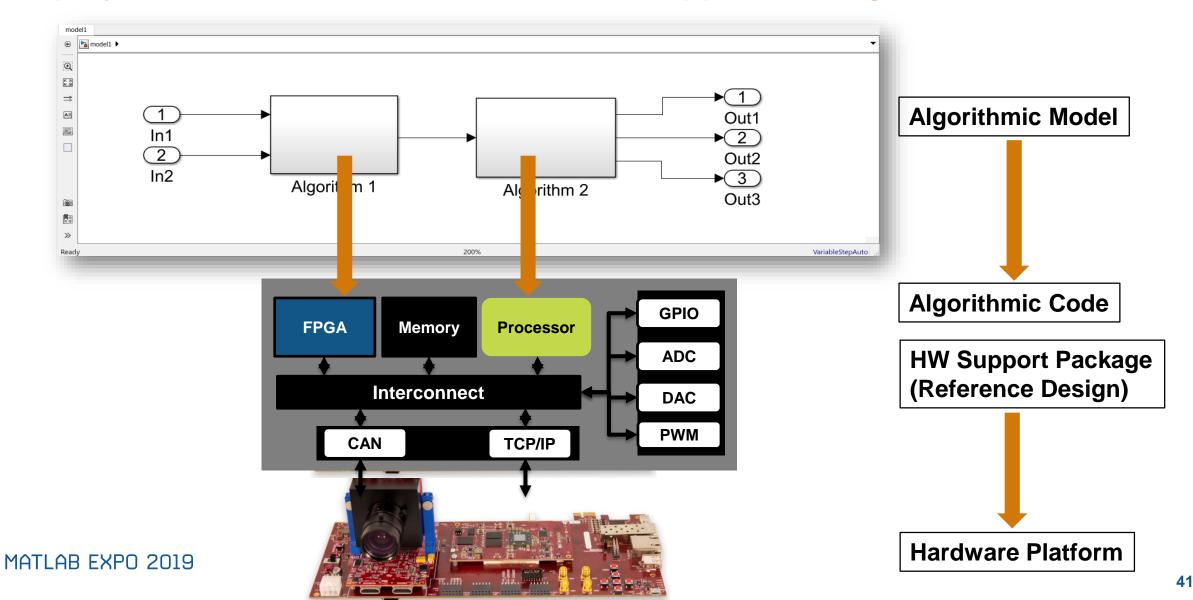

### **Actual Data Exchange Between FPGA and Processor**

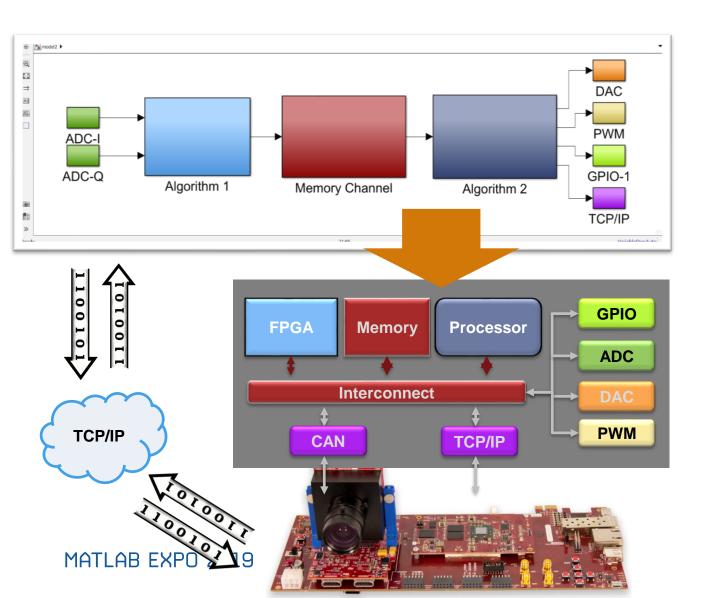

### SoC Blockset / Model and Simulate SoC Architecture

# SoC Blockset / Model and Simulate SoC Architecture

- Simulate algorithms as well as hardware/software architecture

Memory

- Internal/external connectivity

- ► I/O

- Task scheduling

- Deploy on support hardware

- Profile performance using external mode

### SoC Blockset / Example

#### Streaming Data from Hardware to Software

|                                 | Maata an Vialataa         | Aug Complex | Mean Task  | Number     | Frame                                                                                  | Frame                                                                              | 199 #                                                         | (ms)<br>0.05         | 5            |        |

|---------------------------------|---------------------------|-------------|------------|------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------|--------------|--------|

|                                 | Meets or Violates         | Avg Samples | Mean Task  | Number     | Frame                                                                                  | Frame                                                                              | 99 #                                                          | 1                    | 100          | 2      |

|                                 | requirements              | dropped per | Duration   | of buffers | period                                                                                 | Size                                                                               |                                                               | _                    |              | 3      |

|                                 |                           | 10000       | (ms)       |            | (ms)                                                                                   |                                                                                    | eq                                                            | ncy Re               | – Late       | 4<br>5 |

|                                 | Violates throughput       |             | 0.059      | 1999       | 0.05                                                                                   | 5                                                                                  | 4 1                                                           | 20                   | 2000         | 6      |

|                                 | Violates throughput       |             | 1.06       | 99         | 1                                                                                      | 100                                                                                | 3<br><1 2                                                     | 24<br>80             | 2400<br>8000 | 7<br>8 |

|                                 | Violates dron samples     | 172.6       | 7.858      | 11         | 8                                                                                      | 800                                                                                | <1 3                                                          | 180                  | 18000        | 9      |

| •   @, • 🗔 📐   2 <sup>n</sup> t | Meets all requirements    | 0           | 9.61       | 9          | 10                                                                                     | 1000                                                                               | ⊲ 4                                                           | 300                  | 30000        | 10     |

|                                 | Meets all requirements    | 1           | 15.3       | 5          | 16                                                                                     | 1600                                                                               | 5                                                             | 80                   |              |        |

| ſ                               | violates drop samples     | 2.25        | 19.067     | 4          | 20                                                                                     | 2000                                                                               | Б                                                             | 70 -<br>60 -         |              |        |

|                                 | Violates drop samples     | 3.9         | 22.812     | 3          | 24                                                                                     | 2400                                                                               | 7                                                             | (st. 50 -            |              |        |

| r <sup>1</sup>                  | Violates min buffers req  |             | 76.56      | <1         | 80                                                                                     | 8000                                                                               | 8                                                             | u) 40 -              |              |        |

| 50 55 60 65 7                   | Violates min buffers req  |             | 175.23     | <1         | 180                                                                                    | 18000                                                                              | 9                                                             | ي<br><sub>30</sub> - |              |        |

| 10 0100                         | Violates min buffers req  |             | 289.52     | <1         | 300                                                                                    | 30000                                                                              | 10                                                            | 20                   |              |        |

|                                 | 3           2           1 |             | er Channel |            | 7 8 9 1 × 10 <sup>4</sup><br>ory Channel Read Buffer Latency<br>ntaneous Total Latency | 4 5 6<br>Simulation Time (ms)<br>er Latency Mem<br>nowledge Buffer Latency • Insta | 1 2 3<br>Memory Channel Write Buff<br>Memory Channel Read Ack | 00                   |              |        |

MATLAB EXPO 2019

# SoC Blockset / Workflow Summary

#### Simulate SoC Architectures

Develop and combine software algorithms, hardware logic, memory systems, and I/O devices into your SoC application. Evaluate architecture alternatives before deploying to hardware.

### Analyze System Performance

Evaluate memory performance and task execution through simulation and perform on-device profiling.

#### Deploy to SoC and FPGA Devices

Generate reference designs and RTL code for programmable logic. Generate C/C++ code for processor tasks.

#### MATLAB EXPO 2019

### Agenda

- Why Model-Based Design for FPGA, ASIC, or SoC?

- Case Study Pulse Detector

- HW/SW Co-Design

- Customer results

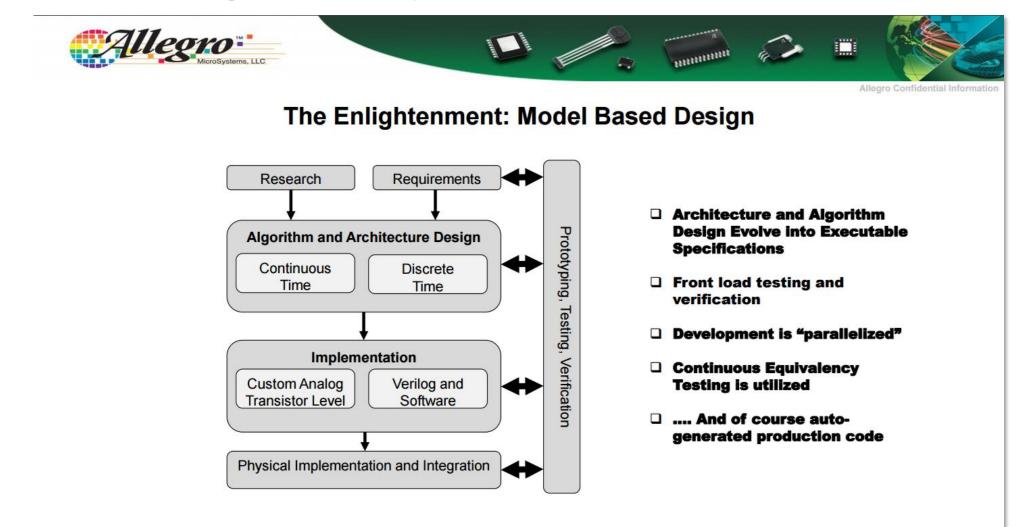

### **Results at Allegro Microsystems**

### **Getting Started Collaborating with Model-Based Design**

- □ Refine algorithm toward implementation

- Verify refinements versus previous versions

- Generate verification models

- Add hardware implementation detail and generate optimized RTL

- □ Simulate System-on-Chip architecture

#### Eliminate communication gaps

- Key decisions made via cross-skill collaboration

- Identify and address system-level issues before implementing subsystems

- Adapt to changing requirements with agility

### Learn More

### • Visit FPGA & SoC booth!

- Next steps to get started with:

- Verification: Improve RTL Verification by Connecting to MATLAB webinar

- Fixed-point quantization: <u>Fixed-Point Made Easy webinar</u>

- Incremental refinement, HDL code generation: <u>HDL self-guided tutorial</u>

- SoC Blockset: <u>Getting Started with SoC Blockset</u>