# MATLAB EXPO 2019

Adopting Model-Based Design for FPGA, ASIC, and SoC Development

Robert Anderson Principal Application Engineer - MathWorks

#### Agenda

#### Why Model-Based Design for FPGA, ASIC, or SoC?

- How to get started

- General approach collaborate to refine with implementation detail

- Re-use work to help RTL verification

- Hardware architecture

- Fixed-point quantization

- HDL code generation

- Chip-level architecture

- Customer results

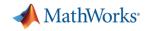

### FPGA, ASIC, and SoC Development Projects

67% of ASIC/FPGA projects are behind schedule

Over 50% of project time is spent on verification

75% of ASIC projects require a silicon re-spin

MATLAB EXPO 2019

## 84% of FPGA projects have non-trivial bugs escape into production

Statistics from 2018 Mentor Graphics / Wilson Research survey, averaged over FPGA/ASIC

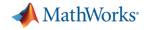

#### Many Different Skill Sets Need to Collaborate

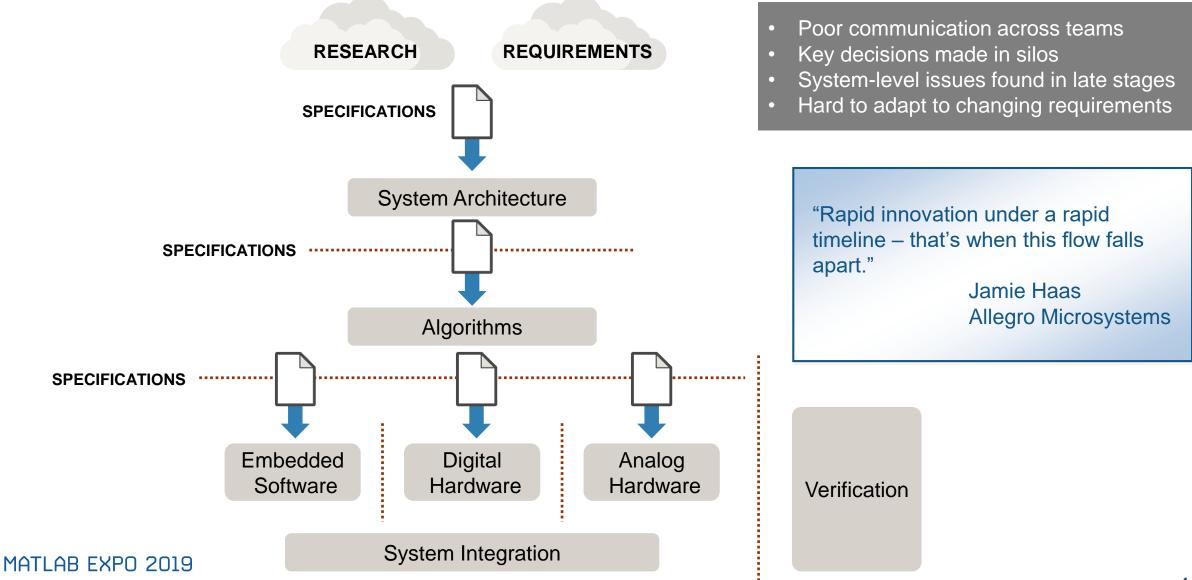

### **Cost of Finding a Bug vs Location in Design Cycle**

Location in Design Cycle

Requirements

High Level Modeling/Verification

Model Elaboration/Fixed-Point Conversion

**RTL Design and HDL Verification**

Place and Route/Floor-planning

Integration and Validation Test

Post – Production/Product Launch

MATLAB EXPO 2019

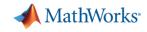

#### **SoC Collaboration with Model-Based Design**

#### Agenda

- Why Model-Based Design for FPGA, ASIC, or SoC?

- How to get started

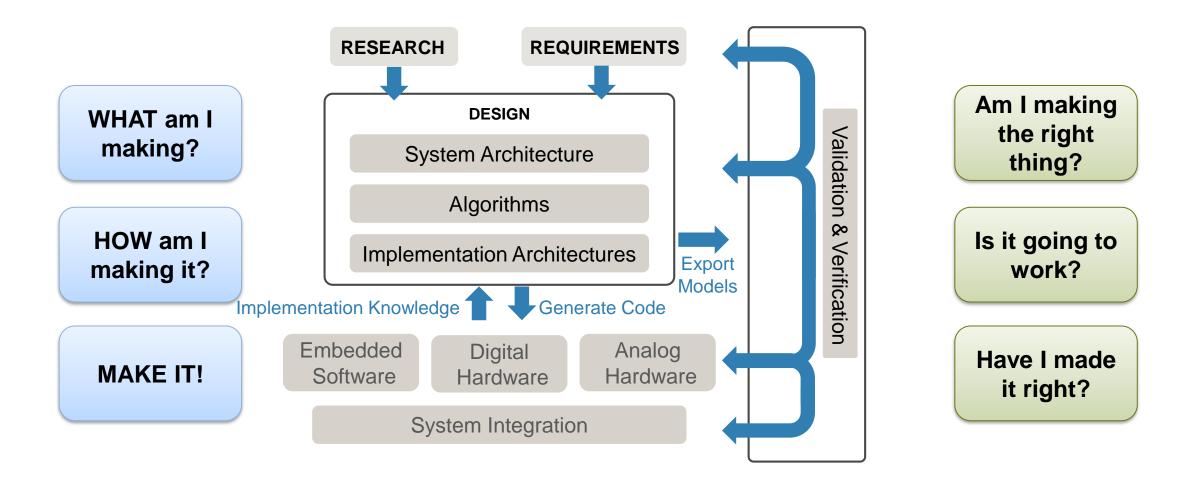

- General approach collaborate to refine with implementation detail

- Re-use work to help RTL verification

- Hardware architecture

- Fixed-point quantization

- HDL code generation

- Chip-level architecture

- Customer results

#### **General Approach: Use the Strengths of MATLAB and Simulink**

- Large data sets

- Explore mathematics

- ✓ Control logic

- Data visualization

- Parallel architectures

- Timing

- Data type propagation

- Mixed-signal modeling

### **Cycle Accurate**

### **Bit Accurate**

### Partition Hardware-Targeted Design, System Context, Testbench

| Algorithm<br>Stimulus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Hardware<br>Algorithm                                                                                                                                                                                                                                                             | Software<br>Algorithm Analysis |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Create input stimulus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MATLAB golden reference                                                                                                                                                                                                                                                           | 1 Tx Signal (real)             |

| <pre>function [ CorrFilter, RxSignal, RxFxPt ] = pulse_detector_stim % Create pulse to detect rng('default'); PulseLen = 64; theta = rand(PulseLen,1); pulse = exp(1i*2*pi*theta); % Insert pulse to Tx signal rng('shuffle'); TxLen = 5000; PulseLoc = randi(TxLen-PulseLen*2); TxSignal = complex(zeros(TxLen,1)); TxSignal(PulseLoc:PulseLoc+PulseLen-1) = pulse; % Create Rx signal by adding noise Noise = complex(randn(TxLen,1),randn(TxLen,1)); RxSignal = TxSignal + Noise; % Scale Rx signal to +/- one scale1_=_max(Labs(real(RxSignal)):.abs(imeg(RxSignal))]);</pre> | <pre>% Create matched filter coefficients<br/>CorrFilter = conj(flip(pulse))/PulseLen;<br/>% Correlate Rx signal against matched filter<br/>FilterOut = filter(CorrFilter,1,RxSignal);<br/>% Find peak magnitude &amp; location<br/>[peak, location] = max(abs(FilterOut));</pre> |                                |

#### MATLAB EXPO 2019

3500

40.00

4500

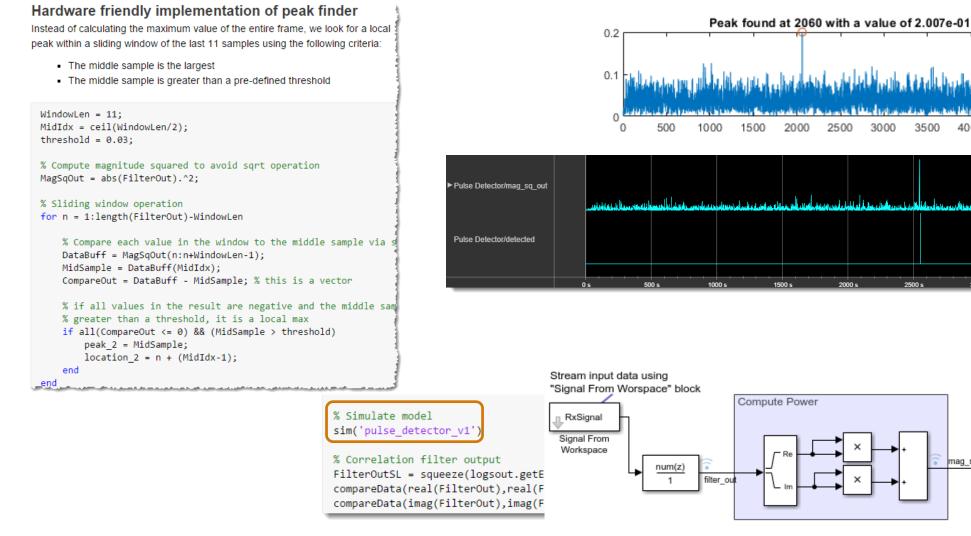

Local Peak

threshold

Constant

11

Tapped Delay

Stores and outputs previous 11 values

Delavs

mag\_sq\_out

5000

4000

threshold

DataBuff

MidSample

detected

fcn

MATLAB Function

### Streaming Algorithms: MATLAB or Simulink...or Both

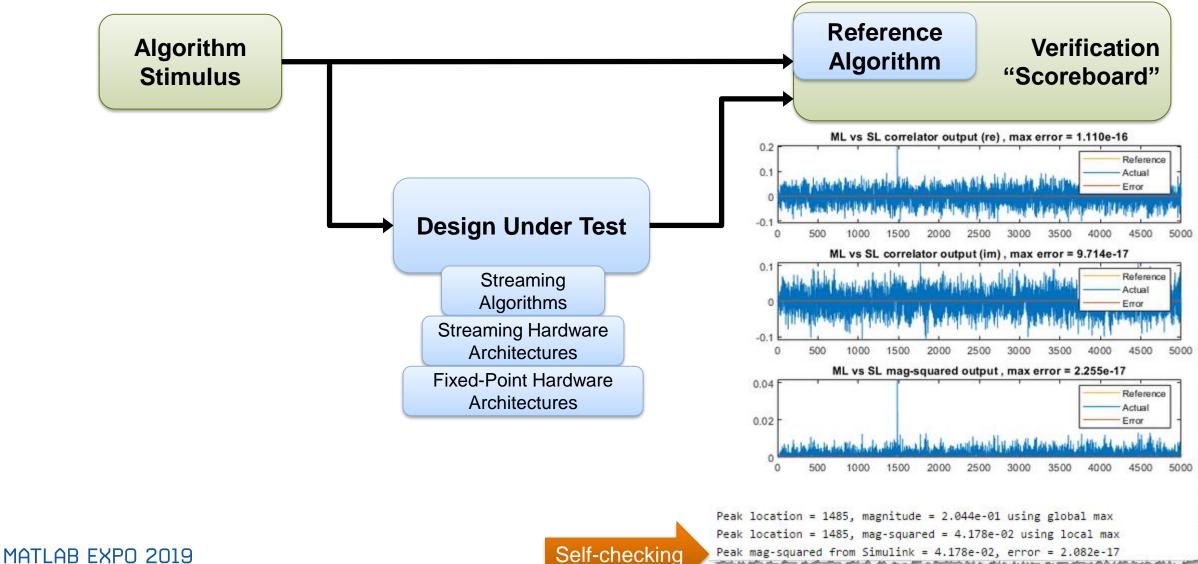

#### **Refine Algorithm and Verify Against Golden Reference**

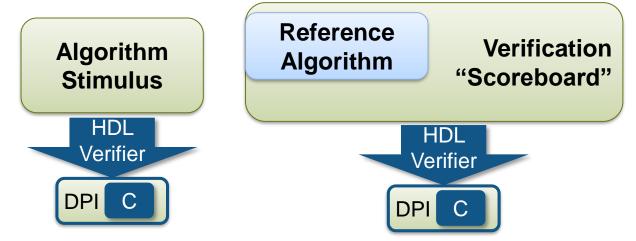

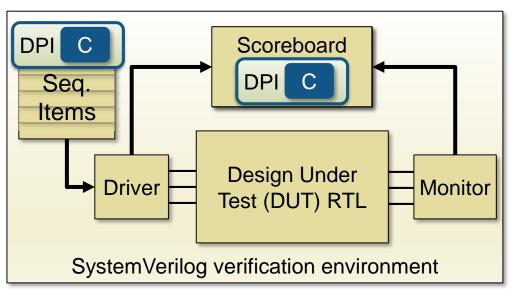

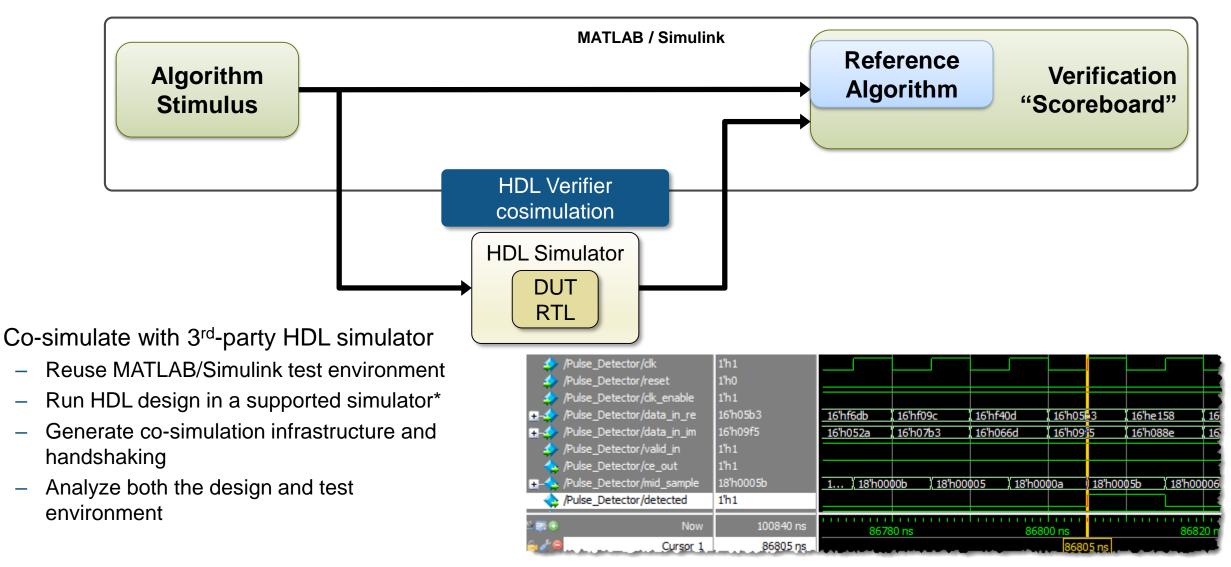

### **Generate SystemVerilog DPI Components for RTL Verification**

- Reuse MATLAB/Simulink models in verification

- Scoreboard, stimulus, or models external to the RTL

- Generate from frame-based or streaming algorithm

- Floating-point or fixed-point

- Individual components or entire testbench

- Runs natively in SystemVerilog simulator

- Eliminate re-work and miscommunication

- Save testbench development time

- Easy to update when requirements change

#### MATLAB EXPO 2019

#### What if there's a mismatch?

#### MATLAB EXPO 2019

\_

—

\_

\* Mentor Graphics® ModelSim® or Questa® Cadence<sup>®</sup> Incisive<sup>®</sup> or Xcelium<sup>™</sup>

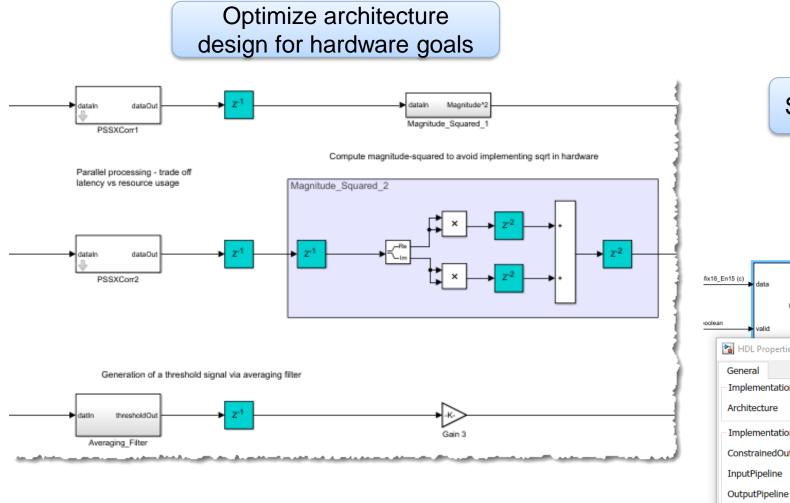

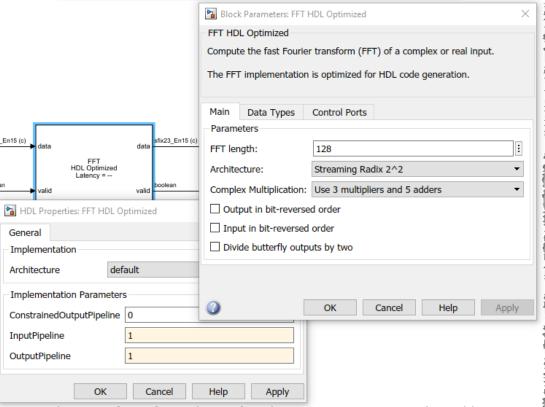

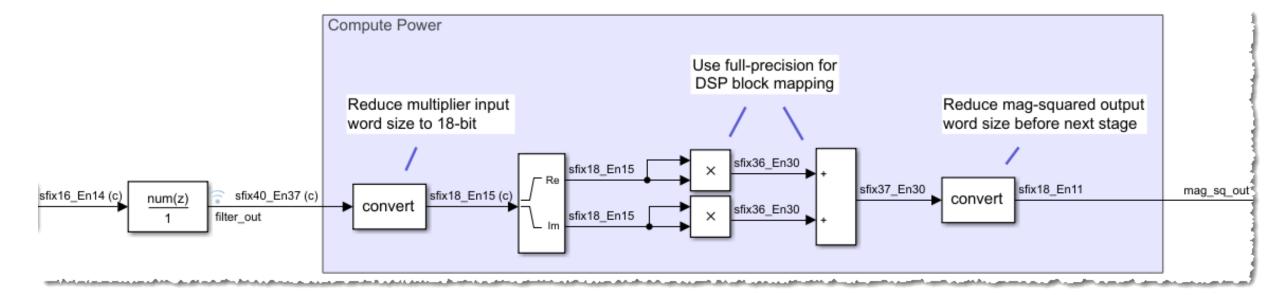

#### **Collaborate to Add Hardware Architecture**

#### Specify HDL implementation options

#### MATLAB EXPO 2019

and an an and an advertising of the second se

#### **Fixed-Point Streaming Algorithms: Manual Approach**

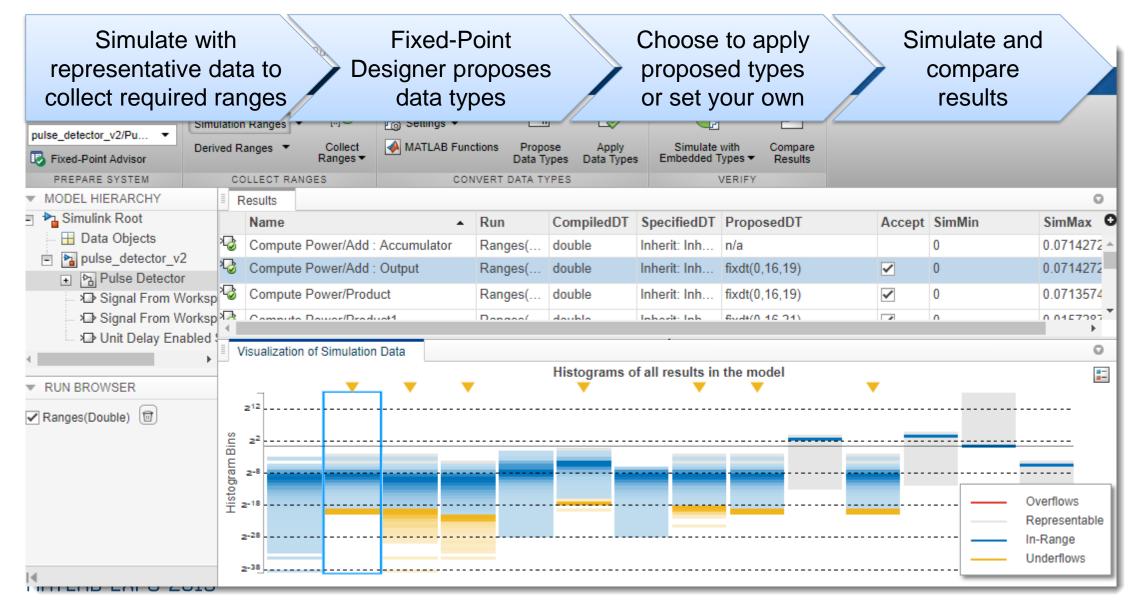

#### **Fixed-Point Streaming Algorithms: Automated Approach**

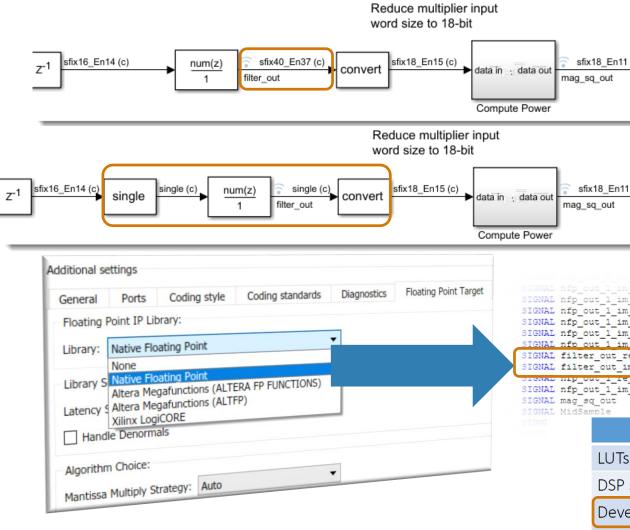

#### **Generating Native Floating Point Hardware**

#### **HDL Coder Native Floating Point**

- Extensive math and trigonometric operator support

- Optimal implementations without sacrificing numerical accuracy

- Mix floating- and fixed-point operations

- Generate target-independent HDL

👥 embeddedaward2017

| SIGNAL nfp_o<br>SIGNAL nfp_o<br>SIGNAL nfp_o<br>SIGNAL nfp_o<br>SIGNAL nfp_o<br>SIGNAL nfp_o<br>SIGNAL filte:<br>SIGNAL filte:<br>SIGNAL nfp_o<br>SIGNAL mag_s<br>SIGNAL MadSa | ut_1_im_94<br>ut_1_im_95<br>ut_1_im_96<br>ut_1_im_97<br>ut_1_im_98<br>r_out_re<br>r_out_re<br>r_out_im<br>dt_1_re_ss<br>ut_1_im_99<br>q_out | <pre>: std_logic_vector(31 D<br/>: std_logic_vector(17 D<br/>: std_logic_vector(17 D<br/>: std_logic_vector(17 D<br/>: std_logic_vector(17 D)</pre> | OWNTO 0);       ufix32         OWNTO 0);       ufix18         OWNTO 0);       ufix18 |                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|                                                                                                                                                                                |                                                                                                                                             | Fixed point                                                                                                                                                                                                                                                                                                                                             | Floating point                                                                                                                                                                                                                                                                                                                                                              |                             |

|                                                                                                                                                                                | LUTs                                                                                                                                        | 10k                                                                                                                                                                                                                                                                                                                                                     | 25k                                                                                                                                                                                                                                                                                                                                                                         |                             |

|                                                                                                                                                                                | DSP slices                                                                                                                                  | 50                                                                                                                                                                                                                                                                                                                                                      | 100                                                                                                                                                                                                                                                                                                                                                                         | ~2x more resources          |

|                                                                                                                                                                                | Development time                                                                                                                            | ~1 week                                                                                                                                                                                                                                                                                                                                                 | ~1 day                                                                                                                                                                                                                                                                                                                                                                      | ~5x less development effort |

|                                                                                                                                                                                |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                             |                             |

#### MATLAB EXPO 2019

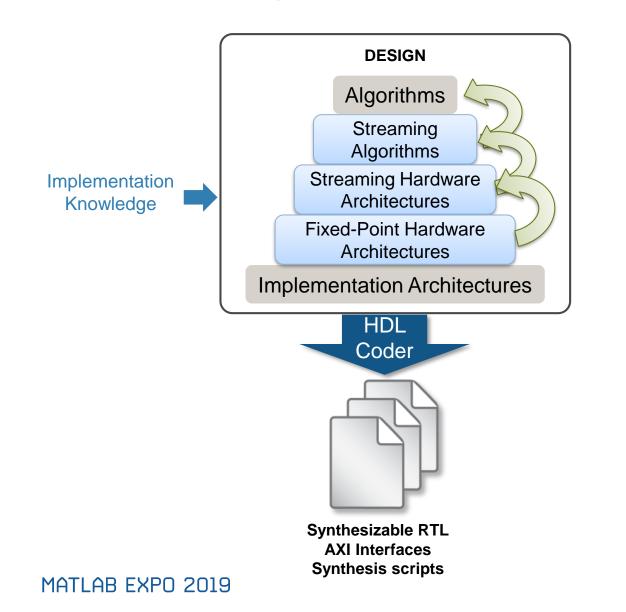

#### **Automatically Generate Production RTL**

- Choose from over 250 supported blocks

- Including MATLAB functions and Stateflow charts

- Quickly explore implementation options

- Micro-architectures

- Pipelining

- Resource sharing

- Fixed-point or native floating point

- Generate readable, traceable Verilog/VHDL

- Optionally generate AXI interfaces with IP core

- Quickly adapt to changes and re-generate

- Production-proven across a variety of applications and FPGA, ASIC, and SoC targets

19

#### Agenda

- Why Model-Based Design for FPGA, ASIC, or SoC?

- How to get started

- General approach collaborate to refine with implementation detail

- Re-use work to help RTL verification

- Hardware architecture

- Fixed-point quantization

- HDL code generation

- Chip-level architecture

- Customer results

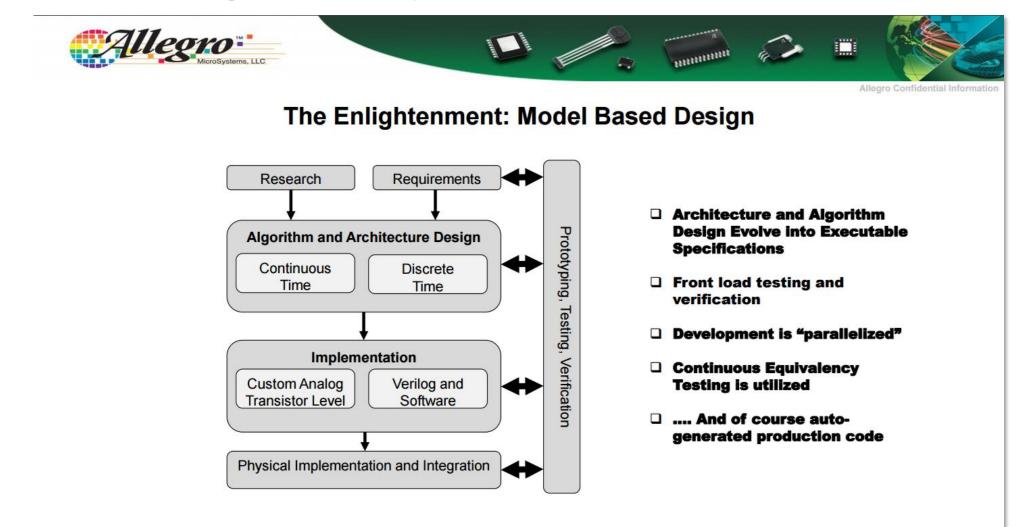

#### **Results at Allegro Microsystems**

#### **Getting Started Collaborating with Model-Based Design**

- Refine algorithm toward implementation

- Verify refinements versus previous versions

- Generate verification models

- Add hardware implementation detail and generate optimized RTL

- □ Simulate System-on-Chip architecture

- Eliminate communication gaps

- Key decisions made via cross-skill collaboration

- Identify and address system-level issues before implementing subsystems

- Adapt to changing requirements with agility

#### **Learn More**

- Next steps to get started:

- Verification: Improve RTL Verification by Connecting to MATLAB webinar

- Fixed-point quantization: <u>Fixed-Point Made Easy webinar</u>

- Incremental refinement, HDL code generation: HDL self-guided tutorial

- https://www.mathworks.com/solutions/fpga-asic-soc-development/asic.html

- Technology showcase here at MATLAB EXPO

- MathWorks Advisory Board (MAB)

- Pilots and Consulting services to help you get on-board

- Contact your local sales representative for hands-on workshops