# MATLAB EXPO 2018

# Hardware and Software Co-Design for Motor Control Applications

#### **Takeaways**

Model-Based Design for SoC FPGAs

- Enables early validation of specifications using simulation

- Improves design team collaboration and designer productivity.

- Reduces hardware testing time by 5x

# Punch Powertrain develops complex SoC-based motor control

- Powertrains for hybrid and electric vehicles

- Need to increase power density and efficiency at a reduced cost

- Integrate motor and power electronics in the transmission

- New switched reluctance motor

- Fast: 2x the speed of their previous motor

- Target to a Xilinx<sup>®</sup> Zynq<sup>®</sup> SoC 7045 device

- Complex: 4 different control strategies

- No experience designing FPGAs!

Link to video of presentation

- Designed integrated E-drive: Motor, power electronics and software

- ✓ 4 different control strategies implemented

- ✓ Completed in 1.5 years with 2FTE's

- ✓ Models reusable for production

- Smooth integration and validation due to development process – thorough validation before electronics are produced and put in the testbench

#### Key trend: Increasing demands from motor drives

- Advanced algorithms require faster computing performance.

- Field-Oriented Control

- Sensorless motor control

- Vibration detection and suppression

- Multi-axis control

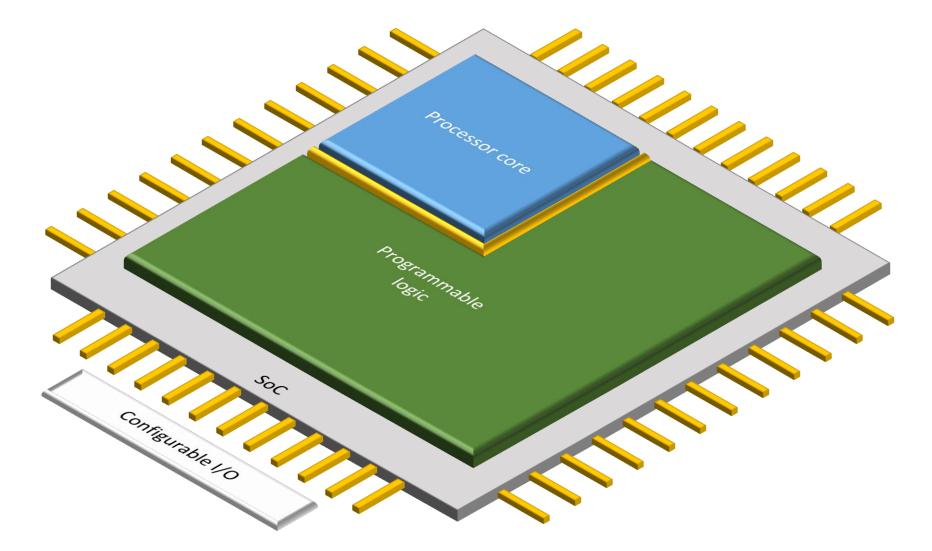

### What's an SoC?

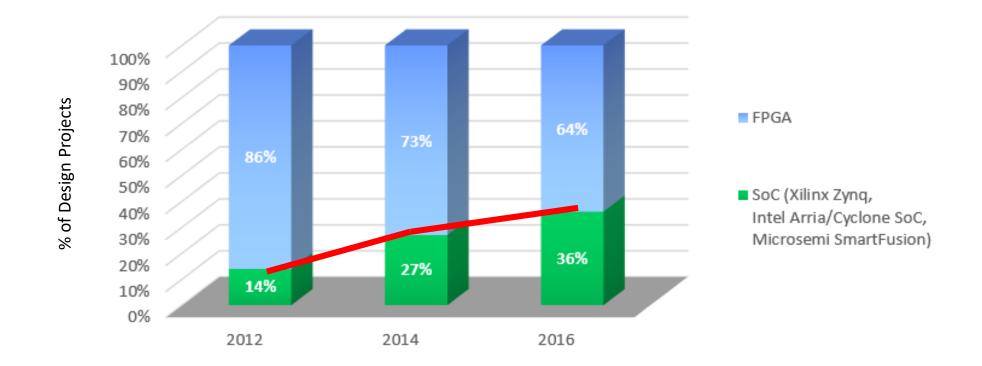

## Key Trend: SoCs are now used in 36% of new FPGA projects

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

### **Challenges in using SoCs for Motor and Power Control**

- Integration of software and hardware partitions of algorithm on SoC drives need for collaboration

- Validation of design specifications with limits on access to motors in labs.

- How to make design decisions that cut across system components?

# Why use Model-Based Design to develop motor control applications on SoCs?

- Enables early validation of specifications using simulation months before hardware is available.

- Improves design team collaboration and designer productivity by using a shared design environment.

- Reduces hardware testing time by 5x by shifting design from lab to the desktop

MATLAB EXPO 2018

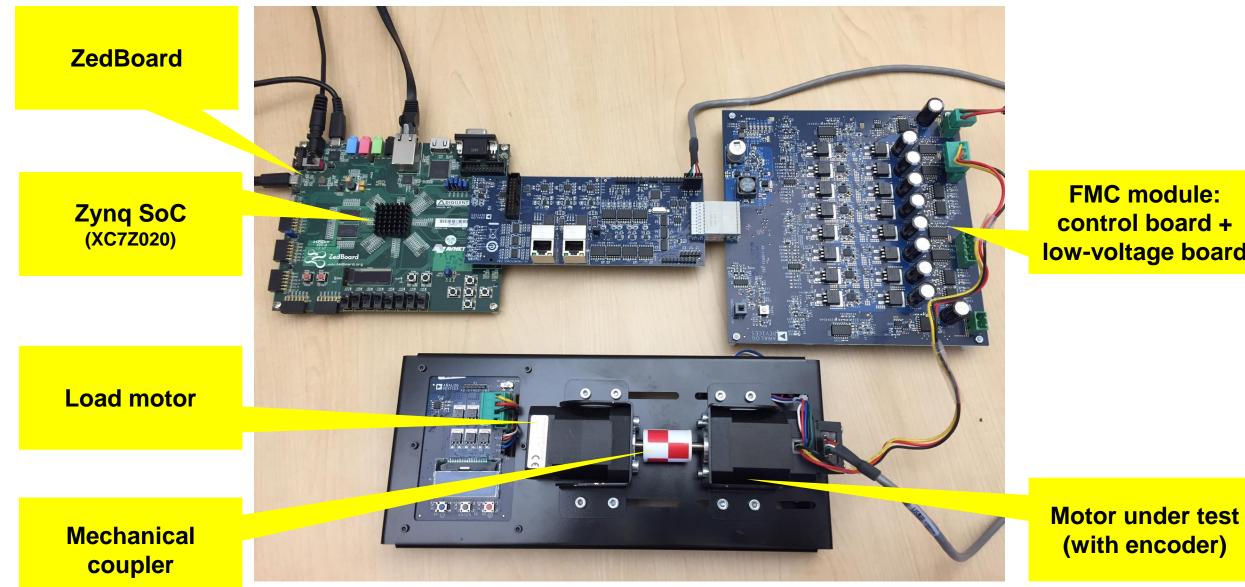

**FMC module:** control board + low-voltage board

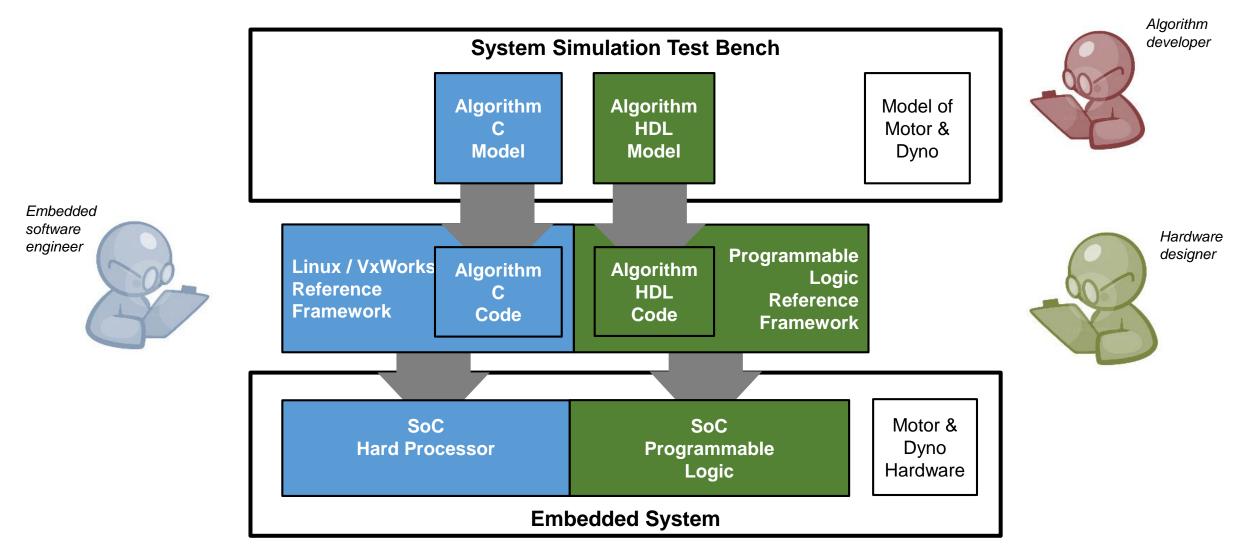

### **Conceptual workflow targeting SoCs**

MathWorks<sup>®</sup>

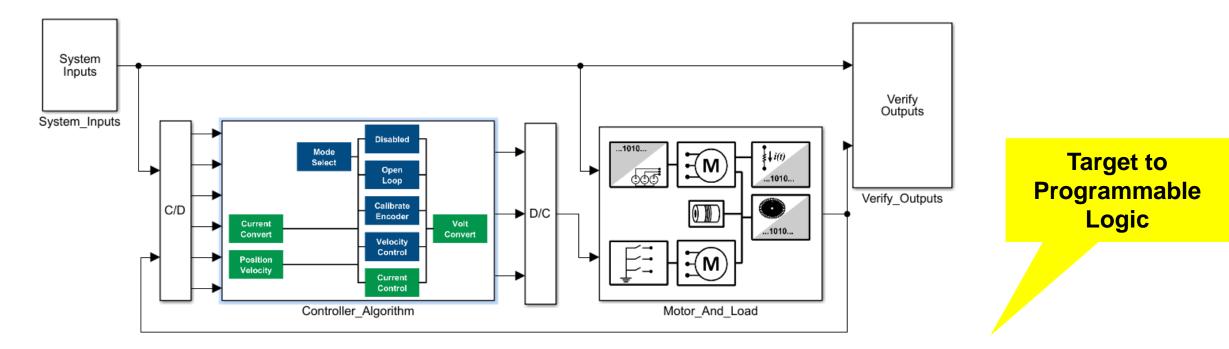

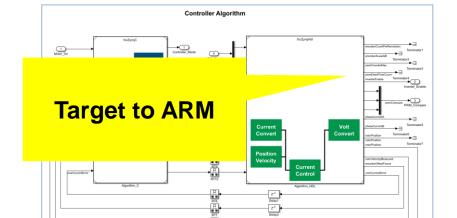

### Hardware/software partitioning

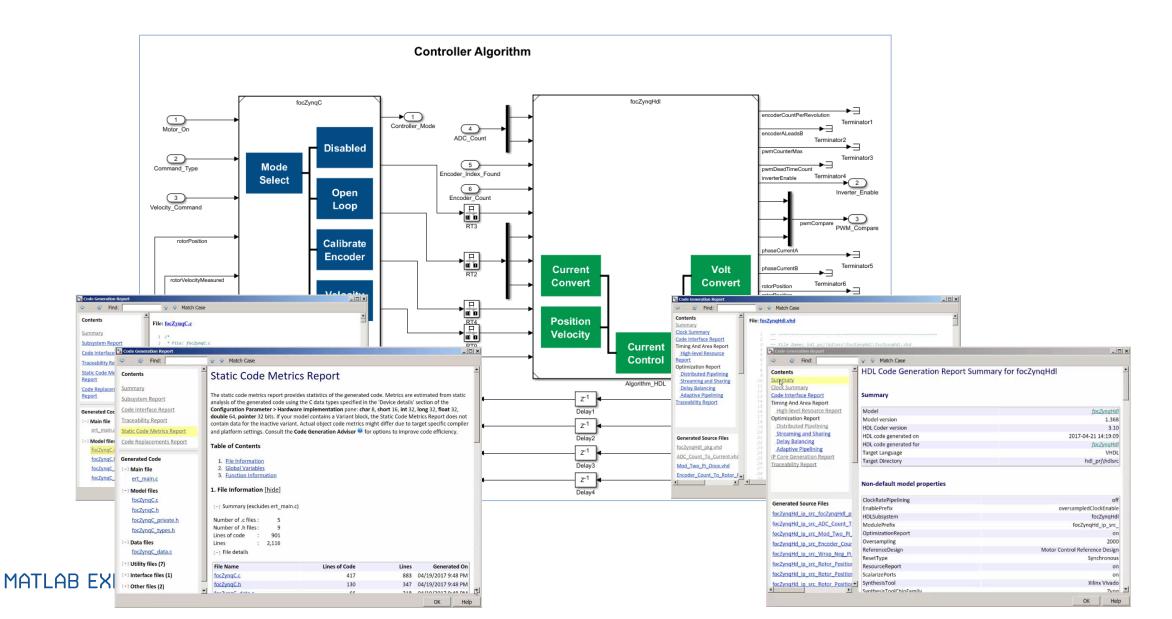

#### **Code Generation**

13

MATLAB EXPO 2018

#### 16

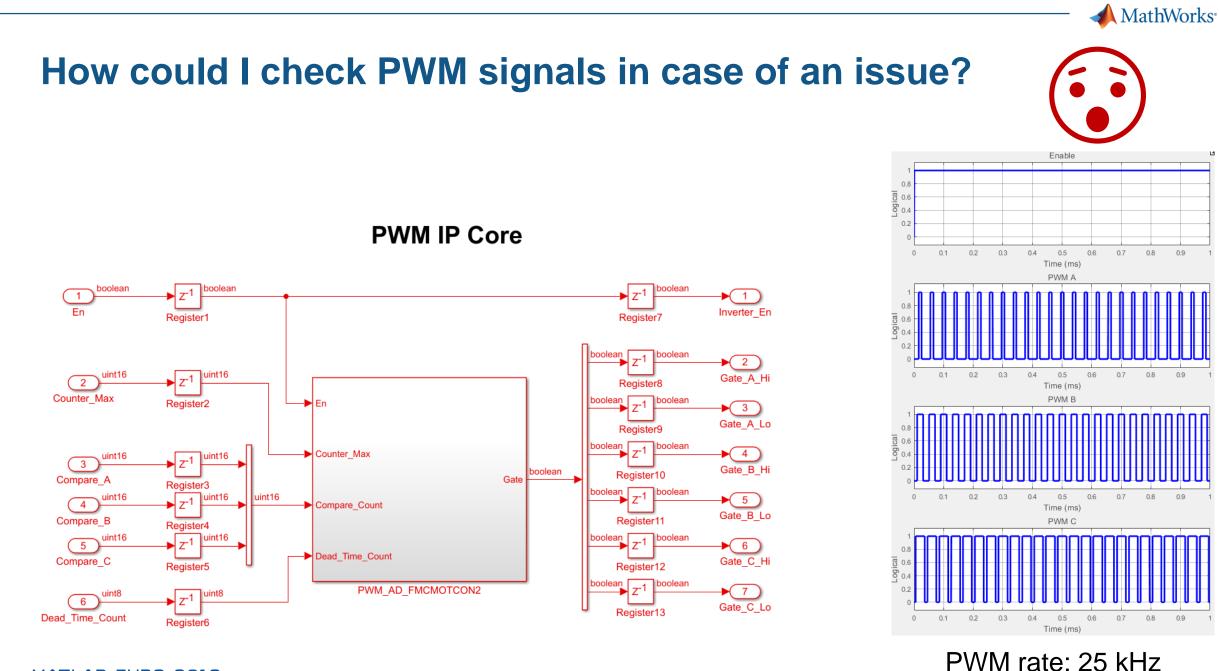

Clock rate: 50 MHz

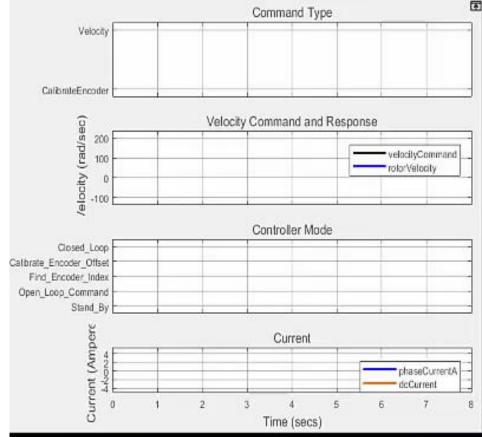

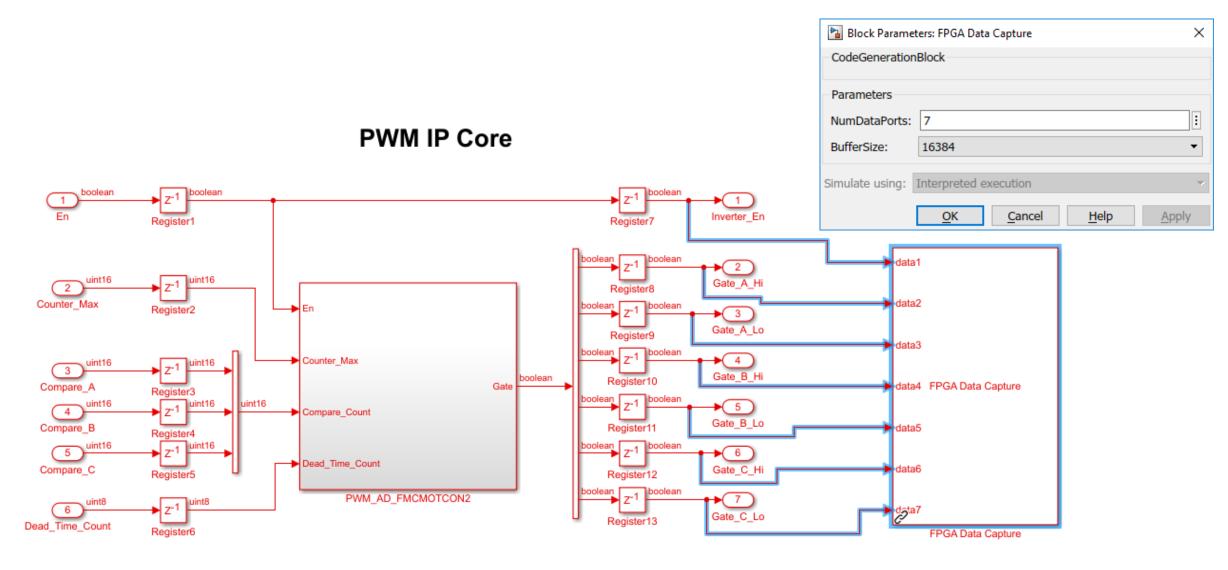

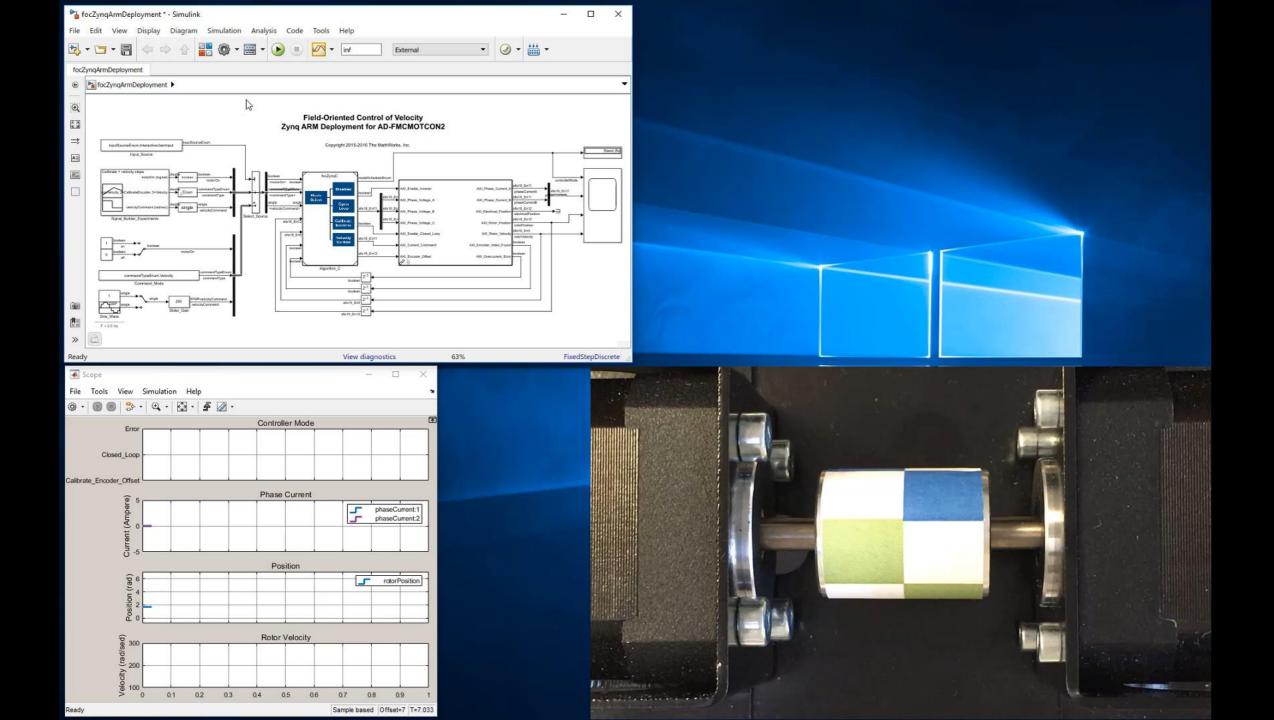

## Add FPGA Data Capture to record 50 MHz outputs from PWMs

| Phase_Voltage_C<br>Enable_Classed_Loop | AXI, Plater, Vedicel, Plater<br>etch Plater<br>AXI, Plater, Vedicel, 2n5<br>biotivAkady<br>biotecen | Number of capture windows: 1                                                        |        |

|----------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------|

| Current, Command                       | ANI_Decade_Index_Fourt                                                                              | Trigger position: 0                                                                 |        |

| ¢                                      |                                                                                                     | Signal Operator Value Change operator                                               |        |

|                                        |                                                                                                     |                                                                                     |        |

|                                        |                                                                                                     | Register7_out1 • +                                                                  |        |

|                                        |                                                                                                     | Status: Successfully captured 1 windows data from FPGA Immediately 🔻 🕨 Capture Data |        |

| 63% T=1                                | 55.683 FixedStepDiscrete                                                                            |                                                                                     |        |

| ×                                      | 🔁 Logic Analyzer                                                                                    | - 1                                                                                 | o x    |

| ĸ                                      | LOGIC ANALYZER TRIGGER WAVE                                                                         |                                                                                     | 6 ?    |

| T                                      |                                                                                                     | Q @                                                                                 |        |

|                                        |                                                                                                     | Find Settings                                                                       |        |

| -1                                     |                                                                                                     | FIND GLOBAL                                                                         | Ā      |

|                                        | Register7_out1 1                                                                                    |                                                                                     |        |

|                                        | Register8_out1 0                                                                                    |                                                                                     |        |

| ent:1<br>ent:2                         | Register9_out1 0                                                                                    |                                                                                     |        |

|                                        | Register10_out1 0                                                                                   |                                                                                     |        |

|                                        | Register11 out1                                                                                     |                                                                                     |        |

| ition                                  | Registe Off time = 610 clock cycles                                                                 |                                                                                     |        |

| ition                                  | Register                                                                                            |                                                                                     |        |

|                                        |                                                                                                     |                                                                                     |        |

|                                        | On time = 1392 clock cycles                                                                         |                                                                                     |        |

|                                        |                                                                                                     |                                                                                     |        |

|                                        | Soo s Cursor 1 O s                                                                                  | 900 s 1200 s 1500 s 1800 s 2100 s 2400 s                                            | 2700 s |

| 1                                      | Cursor 2 525 s 525 s<br>Cursor 3 1917 s                                                             | 1392 S                                                                              |        |

| =155.264                               | Cursor 4 2527 s                                                                                     | 2527 5                                                                              |        |

#### 20

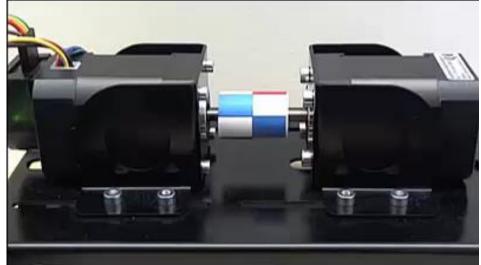

## 3T Develops Robot Emergency Braking System with Model-Based Design

#### Challenge

Design and implement a robot emergency braking system with minimal hardware testing

#### **Solution**

Model-Based Design with Simulink and HDL Coder to model, verify, and implement the controller

#### **Results**

- Cleanroom time reduced from weeks to days

- Late requirement changes rapidly implemented

- Complex bug resolved in one day

"With Simulink and HDL Coder we eliminated programming errors and automated delay balancing, pipelining, and other tedious and error-prone tasks. As a result, we were able to easily and quickly implement change requests from our customer and reduce time-to-market."

Ronald van der Meer

A SCARA robot.

# Why use Model-Based Design to develop motor control applications on SoCs?

# **Challenges:**

- Integration of software and hardware partitions of algorithm on SoC drives need for collaboration

- Validation of design specifications with limits on access to motors in labs.

- How to make design decisions that cut across system?

## Model-Based Design

- Enables early validation of specifications using simulation months before hardware is available.

- Improves design team collaboration and designer productivity by using a shared design environment.

- Reduces hardware testing time by 5x by shifting design from lab to the desktop

#### **Learn More**

Visit us in the Technology Showcase - see Native Floating Point

2 singi Current Comman

- Videos

- HDL Coder: Native Floating Point

- Webinars

- Prototyping SoC-based Motor Controllers on Intel SoCs with MATLAB and Simulink

- How to Build Custom Motor Controllers for Zynq SoCs with MATLAB and Simulink

- Articles

- How Modeling Helps Embedded Engineers Develop Applications for SoCs (MATLAB Digest)

FOC Current Control

ABC single (3) D1

- MATLAB and Simulink Aid HW-SW Codesign of Zynq SoCs (Xcell Software Journal)

- Tutorials:

- <u>Custom Reference Design Workflow for HDL Coder</u>

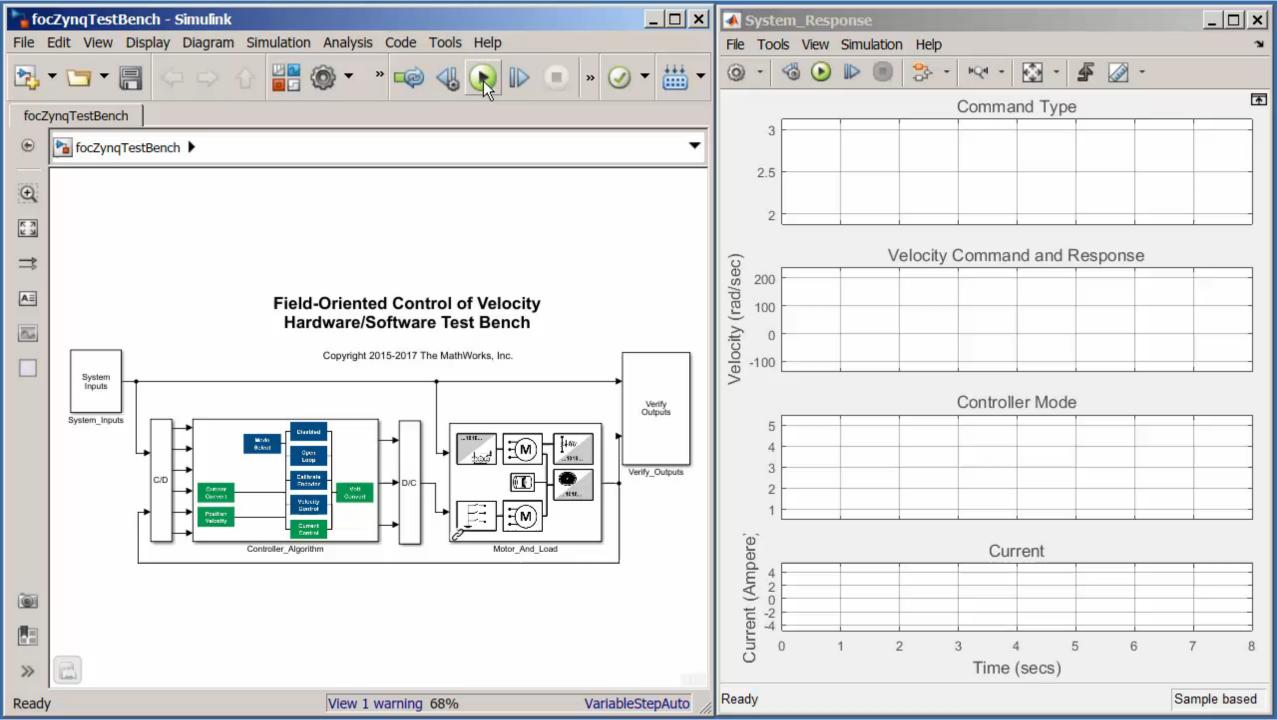

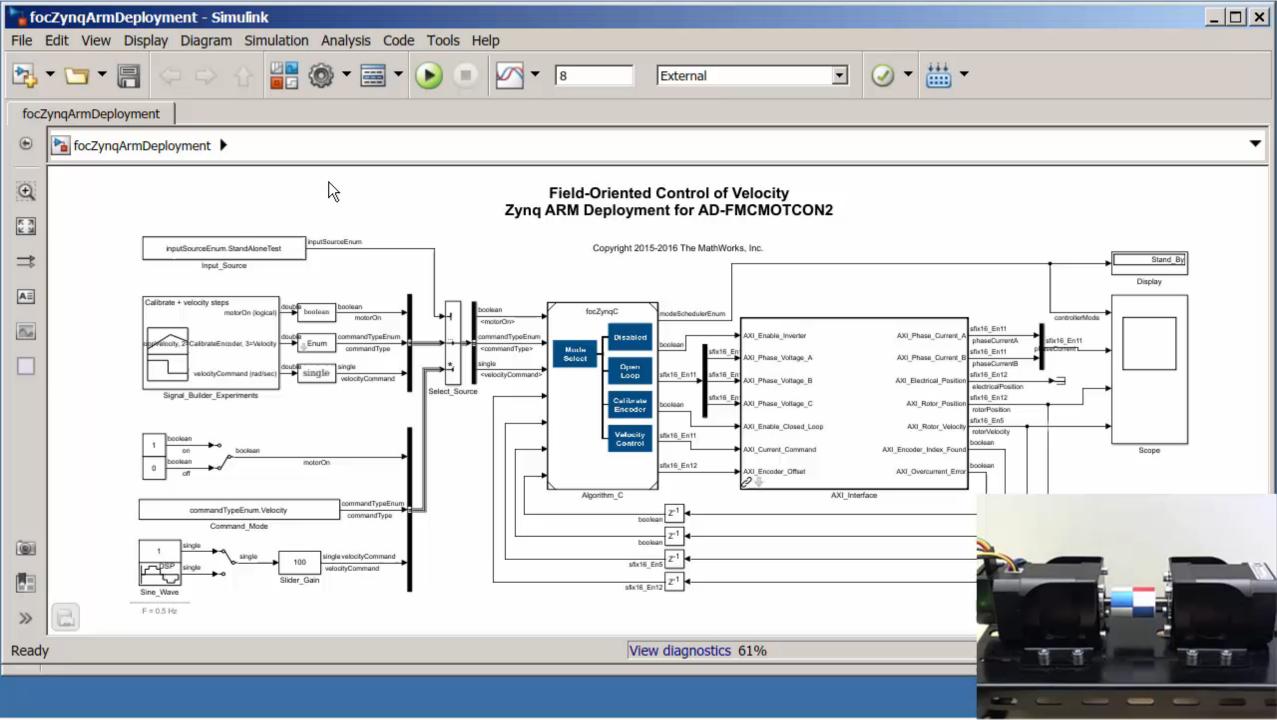

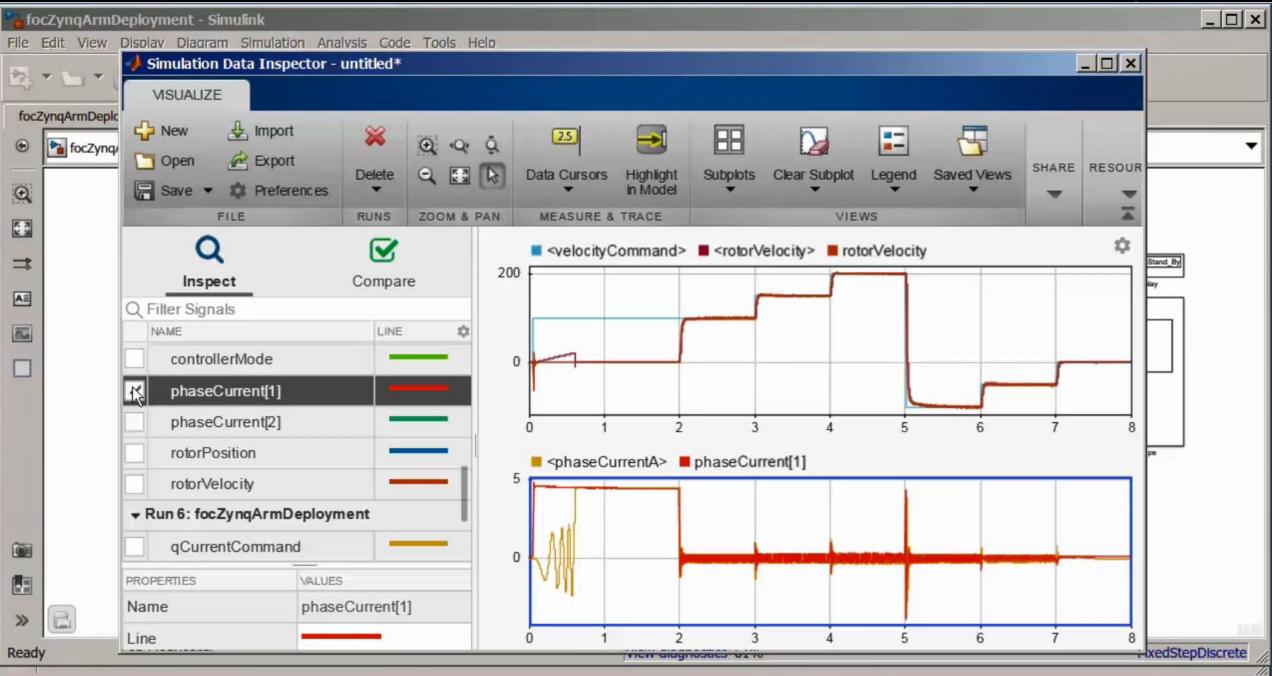

- Field-Oriented Control of a Permanent Magnet Synchronous Machine on SoCs